# Clock Domain Crossing Standard Version 0.5 Draft for Public Review

4

7

April 14, 2025

2 Abstract: In-house and externally purchased IPs are often combined in SOCs. It can prove chal3 lenging to verify these SOCs because a mixture of verification tools and methodologies that do not

4 integrate can be used. Ensuring that a common clock domain crossing interface standard that

5 every tool can translate their native format to and from is the intent of this standard. With this inter6 face standard, every IP developer's verification tool of choice is run to verify and produce collat7 eral, and the standard format is generated for SOCs that used a different tool. And with this

8 standard, efficiently translating from provided collateral into a tool of choice is possible for every

9 SOC. A way to specify all the information necessary to do accurate clock domain crossing, reset

10 domain crossing, and glitch structural analysis is afforded. Attributes for a block that can be used

11 to facilitate a correct clock domain crossing and reset domain crossing integration of that block in

12 an encompassing design are identified. The limitations of the set of attributes are also addressed;

13 that is, the clock domain crossing and reset domain crossing schemes for which the set of attri14 butes is sufficient and the schemes the defined set of attributes is not guaranteed to support are

15 identified.

**17 Keywords:** CDC, clock domain crossing, glitch, IP-XACT, RDC, reset domain crossing, functional **18** verification.

**31** AMBA® is a registered trademark of Arm® Limited (or its subsidiaries) in the US and/or elsewhere

1 Notices

2 Accellera Systems Initiative (Accellera) Standards documents are developed within Accellera and the 3 Technical Committee of Accellera. Accellera develops its standards through a consensus development pro-4 cess, approved by its members and board of directors, which brings together volunteers representing varied 5 viewpoints and interests to achieve the final product. Volunteers are members of Accellera and serve without 6 compensation. While Accellera administers the process and establishes rules to promote fairness in the con-7 sensus development process, Accellera does not independently evaluate, test, or verify the accuracy of any 8 of the information contained in its standards.

Use of an Accellera Standard is wholly voluntary. Accellera disclaims liability for any personal injury, prop- erty or other damage, of any nature whatsoever, whether special, indirect, consequential, or compensatory, directly or indirectly resulting from the publication, use of, or reliance upon this, or any other Accellera Standard document.

13 Accellera does not warrant or represent the accuracy or content of the material contained herein, and 14 expressly disclaims any express or implied warranty, including any implied warranty of merchantability or 15 suitability for a specific purpose, or that the use of the material contained herein is free from patent infringe-16 ment. Accellera Standards documents are supplied "AS IS."

17 The existence of an Accellera Standard does not imply that there are no other ways to produce, test, measure, 18 purchase, market, or provide other goods and services related to the scope of an Accellera Standard. Further-19 more, the viewpoint expressed at the time a standard is approved and issued is subject to change due to 20 developments in the state of the art and comments received from users of the standard. Every Accellera 21 Standard is subjected to review periodically for revision and update. Users are cautioned to check to deter-22 mine that they have the latest edition of any Accellera Standard.

23 In publishing and making this document available, Accellera is not suggesting or rendering professional or 24 other services for, or on behalf of, any person or entity. Nor is Accellera undertaking to perform any duty 25 owed by any other person or entity to another. Any person utilizing this, and any other Accellera Standards 26 document, should rely upon the advice of a competent professional in determining the exercise of reasonable 27 care in any given circumstances.

28 Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they 29 relate to specific applications. When the need for interpretations is brought to the attention of Accellera, 30 Accellera will initiate action to prepare appropriate responses. Since Accellera Standards represent a consensus of concerned interests, it is important to ensure that any interpretation has also received the concurrence 32 of a balance of interests. For this reason, Accellera and the members of its Technical Committees are not 33 able to provide an instant response to interpretation requests except in those cases where the matter has pre-34 viously received formal consideration.

Comments for revision of Accellera Standards are welcome from any interested party, regardless of mem- bership affiliation with Accellera. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Comments on standards and requests for interpretations should be addressed to:

Accellera Systems Initiative.

8698 Elk Grove Blvd Suite 1, #114

Elk Grove, CA 95624

USA

NOTE—Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. Accellera shall not

- 1 be responsible for identifying patents for which a license may be required by an Accellera standard

- 2 or for conducting inquiries into the legal validity or scope of those patents that are brought to its

- 3 attention.

- 4 Accellera is the sole entity that may authorize the use of Accellera-owned certification marks and/or trade-5 marks to indicate compliance with the materials set forth herein.

- 6 Authorization to photocopy portions of any individual standard for internal or personal use must be granted

- 7 by Accellera, provided that permission is obtained from and any required fee is paid to Accellera. To arrange

- 8 for authorization please contact Lynn Garibaldi, Accellera Systems Initiative, 8698 Elk Grove Blvd Suite 1,

- **9**#114, Elk Grove, CA 95624, phone (916) 670-1056, e-mail lynn@accellera.org. Permission to photocopy **10** portions of any individual standard for educational classroom use can also be obtained from Accellera.

- 11 Suggestions for improvements to the Clock Domain Crossing Standard 0.5 Draft for Public Review are wel-12 come. They should be posted to the Clock Domain Crossing (CDC) community forum at:

- https://forums.accellera.org/forum/56-cdc-draft-lrm-release-discussion/

- 14 The current Working Group (WG) web page is:

- https://accellera.org/activities/working-groups/clock-domain-crossing

## <sub>1</sub> Participants

41

2 The CDC WG operates on an entity-based model. The following registered members have made contribu-3 tions to the standard at various milestones or participated in the workgroup as observers.

| 4                          |                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5                          | Lee Fueng Yap, Intel Corporation, Chair                                                                                                                                                                                                                                                                                                                                                  |

| 6                          | Sean ODonohue, Synopsys Inc, Vice-Chair                                                                                                                                                                                                                                                                                                                                                  |

| 7                          | Farhad Ahmed, Siemens EDA, Secretary                                                                                                                                                                                                                                                                                                                                                     |

| 8                          |                                                                                                                                                                                                                                                                                                                                                                                          |

| 9                          | Agnisys, Inc: Aiyush Aggarwal, Anupam Bakshi, Devendra Gupta, Devender Khari, Yogita                                                                                                                                                                                                                                                                                                     |

| 10<br>11                   | Koli,Pinku Kumar, Raushan Kumar, Sunil Kumar, Mayank Nigam, Abhinandan Reddy,Vineet Sharma, Rajiv Singh, Sahil singh                                                                                                                                                                                                                                                                     |

| 12                         | AMD: Apoorv Aggarwal, David Courtright, Vishwanath Sundararaman, Jia Zhu                                                                                                                                                                                                                                                                                                                 |

| 13<br>14                   | <b>ARM, Ltd.</b> : Haralds Capkevics, Ravi Teja Chatta, Edwin Dankert, Sylvain Duvillard, Ramya Sri Murugesan, Pat Overs, Stephen Hill, David Murray, Peter Riocreux, Xiaodong Zhuang                                                                                                                                                                                                    |

| 15                         | Arteris, Inc.: Said Derradji, Pawel Duc                                                                                                                                                                                                                                                                                                                                                  |

| 16                         | Blue Pearl Software, Inc.: Jeffery Chan, Bill Gascoyne, David Wallace                                                                                                                                                                                                                                                                                                                    |

| 17<br>18<br>19             | Cadence Design Systems, Inc.: Pradeep B, Luis Humberto Rezende Barbosa, Aparna Dey, Larry Lai, Shivaji Magadum, Greg Milano, Mamta Parab, Sundara Rajan, Souradip Sarkar, Anshuman Seth, Konrad Sikora                                                                                                                                                                                   |

| 20<br>21<br>22<br>23<br>24 | Infineon Technologies: John Jebakumar, Ambuja Rashinkar, Joachim Voges, Joseph Yackzar Intel Corporation: Jeremy Anderson, Boon Chong Ang, Mallikarjuna Badam, Amol Bhinge, Lauren Carlson, Saransh Choudhary, Sharvil Desai, Pawel Duc, Eldad Falik, Sachin Jain, Dinesh M. William Mok, Ravindra Nibandhe, Iredamola Olopade, ATif Razak, Rohit Sinha, Chee Yoong Tan Lee, Jebin Vijai |

| 25                         | Marvell International, Ltd.: Sam Bueti, Gaurav Chhabra, Thien Le, Chetan Choppali Sudarshan                                                                                                                                                                                                                                                                                              |

| 26                         | Microchip Technology Inc.: Don Mills                                                                                                                                                                                                                                                                                                                                                     |

| 27                         | Microsoft Corporation: Shelly Henry, Serena Badran-Louca                                                                                                                                                                                                                                                                                                                                 |

| 28                         | NVIDIA Corporation: Sangeetha Sudha Nakerikanti, Kuan-I Wu, Ping Yeung,                                                                                                                                                                                                                                                                                                                  |

| 29                         | <b>NXP Semiconductors</b> : Inayat Ali, Lei Deng, Vishal Jain, Shweta Pujar, Sasa Ristic, Gaurav Saini                                                                                                                                                                                                                                                                                   |

| 30                         | Qualcomm Incorporated: Suman Chalana, Eric Jackowski, Prasad Nandipati                                                                                                                                                                                                                                                                                                                   |

| 31<br>32                   | Renesas Electronics Corp.: Kaiwen Chin, Ciro Ceissler, Kantha Bheemireddygari, Abhay Kejriwal, Kranthi Pamarthi, Esra Sahin Basaran, Fengzhou Wang                                                                                                                                                                                                                                       |

| 33                         | Robert Bosch GmbH: Jan Hayek, liu kay                                                                                                                                                                                                                                                                                                                                                    |

| 34<br>35                   | <b>Siemens EDA</b> : Farhad Ahmed, Abdelouahab Ayari, Manish Bhati, Abdul Moyeen, Andrew Seawright, Yuxin You                                                                                                                                                                                                                                                                            |

| 36                         | STMicroelectronics: Jean-Christophe Brignone, Diana Kalel, Kenan Kaplan, Laurent Maillet-Con-                                                                                                                                                                                                                                                                                            |

| 37                         | toz,                                                                                                                                                                                                                                                                                                                                                                                     |

| 38                         | Julian Massicot, Ashish Soni                                                                                                                                                                                                                                                                                                                                                             |

| 39                         | Synopsys, Inc.: Jerome Avezou, Sudeep Mondal, Sean ODonohue, Suresh Barla, Tai Vo                                                                                                                                                                                                                                                                                                        |

| 10                         | Texas Instruments, Inc.: Lakshmanan Balasubramanian, Abhinav Parashar                                                                                                                                                                                                                                                                                                                    |

|                            |                                                                                                                                                                                                                                                                                                                                                                                          |

1 At the time of standardization, the CDC WG had the following eligible voters:

Agnisys, Inc. Microsoft

ARM Limited QualcommTechnologies, Inc.

Blue Pearl Software Renesas Electronics Corp.

Infineon Technologies AG Siemens EDA

Intel Corporation STMicroelectronics N.V.

Marvell Technology, Inc. Synopsys, Inc.

2

1

This introduction is not part of IEEE P XXXX-20XX, IEEE Draft Standard for....

#### 3 Introduction

4 The purpose of this standard is to provide the electronic design automation (EDA), semiconductor, and 5 system design communities with a well-defined specification for unified handling of CDC by vendor tools 6 used across IPs and SOCs.

7 Industry design style can be largely classified into two types (not exhaustive), namely:

- Monolithic design: The entire product and its various hierarchies are all designed by one team. All 8 aspects of the design are accessible (and editable) by that team. This type requires knowledge and 9 expertise of all aspects of the design but provides control and autonomy over all aspects of the 10 design (including tools and methodology). Depending on how extensive the product is, and how 11 large (or small) the team is, this style can require a considerable time investment. 12

- **IP/SOC design:** The product is composed of various IPs that can be designed in-house (by this 13 team, or another team) or purchased externally. This means that the required knowledge and exper-14 tise of all aspects of the design are not available in the SOC team, and as a result, the SOC team has 15 less autonomy and control over all aspects of the design. This style can significantly accelerate prod-16 17 uct development depending on the quality of the IPs and how easy it is to integrate into the product SOC. 18

- 19 NOTE—Most of the industry is shifting from monolithic design styles to IP/SOC design styles, and many IP companies 20 provide their IP to multiple SOC product companies. In addition, there is no expectation that every IP and every SOC 21 company is using the same tools and methodology for validating the design, including CDC analysis.

- 22 For most collateral types (for example, SystemVerilog, cluster test environment, low power, and so forth), 23 there exist standards that govern its use; hence, integration for these types of collateral has been largely 24 straight-forward. But for CDC collateral the industry has not had a clean way to handle tool and 25 methodology differences across IPs and SOCs.

- 26 The following list describes various methods of handling the differences in the absence of this standard **27** proposal:

- Monolithic SOC design: Gives tool and methodology autonomy but delays time-to-market. 28 a)

- Black-boxing IP: Assumes the IP is clean and ignores checking for integration issues by black-box-29 b) ing. This helps with initial time-to-market but introduces quality risks that can lead to silicon re-30 spin, which eventually impacts the product's time-to-market.

- Re-verification of IP: Re-verifies IPs on CDC tools that might be different from those used by the IP 32 provider. These teams lack the knowledge and expertise to do a thorough and efficient job, thus put-33 ting both time-to-market and quality at risk, even after employing considerable resources and effort. 34

- Common tools between SOC and IPs: Requests all IP companies they purchase from provide collat-35 eral analyzed with their tool of choice. In this scenario, IP companies that provide IP to different 36 SOC companies must run multiple tools to fit all SOC needs. Even if the IP company agrees, they 37 38 push back on their delivery date to master new tools and collateral, which eventually impacts SOC time-to-market. 39

- 1 None of the approaches above is able to provide sufficient quality in reasonable time. However, defining a

- 2 standard format to capture clock domain crossing (CDC), reset domain crossing (RDC), and glitch intent

- **3** enables interoperability of CDC collateral generated by any CDC verification tool.

## **₁ Contents**

| 41.           | Over       | view       |                                                               | 13 |

|---------------|------------|------------|---------------------------------------------------------------|----|

| 5             | 1.1        | Scope.     |                                                               | 13 |

| 6             | 1.2        | Purpos     | se                                                            | 14 |

| 7             | 1.3        |            | ntions used                                                   |    |

| 8             |            | 1.3.1      | Circuit drawing conventions                                   | 14 |

| 9             |            | 1.3.2      | Word usage                                                    | 16 |

| 10            | 1.4        | Use of     | color in this standard                                        | 16 |

| 11            | 1.5        | Conten     | ts of this standard                                           | 16 |

| 12 2.         | Refe       | rences     |                                                               | 17 |

| 13 3.         | Defin      | nitions, a | acronyms, and abbreviations                                   | 18 |

| 14            | 3.1        | Definit    | ions                                                          | 18 |

| 15            | 3.2        | Acrony     | ms and abbreviations                                          | 18 |

| 16 4.         | CDC        | Attribu    | tes                                                           | 20 |

| 17            | 4.1        | Module     | e attribute                                                   | 30 |

| 18            | 4.2        | Parame     | eter attributes                                               | 30 |

| 19            | 4.3        | Port att   | tributes                                                      | 33 |

| 20            |            | 4.3.1      | Port attributes: name, direction, and type                    | 33 |

| 21            |            | 4.3.2      | Port attribute: associated_from_clocks                        | 34 |

| 22            |            | 4.3.3      | Port attributes: associated_to_clocks                         | 36 |

| 23            |            | 4.3.4      | Defining a virtual clock                                      |    |

| 24            |            | 4.3.5      | Port attribute: associated_from_reset and associated_to_reset |    |

| 25            |            | 4.3.6      | Port attribute: ignore                                        |    |

| 26            |            | 4.3.7      | Port attribute: cdc_static                                    |    |

| 27            |            | 4.3.8      | Port attribute: constant                                      |    |

| 28            |            | 4.3.9      | Port attribute: associated_outputs                            |    |

| 29            |            | 4.3.10     | Port attribute: logic                                         |    |

| 30            | 4.4        | • –        | reset                                                         |    |

| 31            | 4.5        |            | ing abstracted blocks                                         |    |

| 32            | 4.6        |            | definitions                                                   |    |

| 33<br>34      | 4.7<br>4.8 |            | relationships modes                                           |    |

| 35 <b>5</b> . | Supp       | ort for F  | RDC verification                                              | 75 |

|               |            |            |                                                               |    |

| 36            | 5.1        | -          | ements for IP with control outside the IP                     |    |

| 37            |            | 5.1.1      | Scenario 1                                                    |    |

| 38            |            | 5.1.2      | Scenario 2                                                    |    |

| 39            |            | 5.1.3      | Scenario 3                                                    |    |

| 40            | 5.2        | 5.1.4      | Scenario 4ements for IP with control within the IP            |    |

| 41            | 5.2        | 5.2.1      | Scenario 1                                                    |    |

| 42            |            | 5.2.1      | Scenario 2                                                    |    |

| 43<br>44      |            | 5.2.3      | Scenario 3                                                    |    |

| 77            |            | ر.د.       | Deviluate J                                                   |    |

| 1                 |                    | 5.2.4 Scenario 4                                                        | 87  |

|-------------------|--------------------|-------------------------------------------------------------------------|-----|

| 2                 |                    | 5.2.5 Scenario 5                                                        | 90  |

| з 6.              | CDO                | C TCL format                                                            | 91  |

| 4                 | 6.1                | cdc set module                                                          | 91  |

| 5                 |                    | 6.1.1 Syntax example                                                    |     |

| 6                 | 6.2                | cdc set port                                                            | 91  |

| 7                 |                    | 6.2.1 Syntax example                                                    | 92  |

| 8                 | 6.3                | cdc_set_clock_group                                                     | 93  |

| 9                 |                    | 6.3.1 Syntax example                                                    | 94  |

| 10                | 6.4                | cdc_set_param                                                           | 94  |

| 11                |                    | 6.4.1 Syntax example                                                    | 94  |

| 12 7.             | CDO                | C IP-XACT format                                                        | 96  |

| 13                | 7.1                | Top-level elements                                                      |     |

| 14                | 7.2                | Top element—accellera:wire                                              |     |

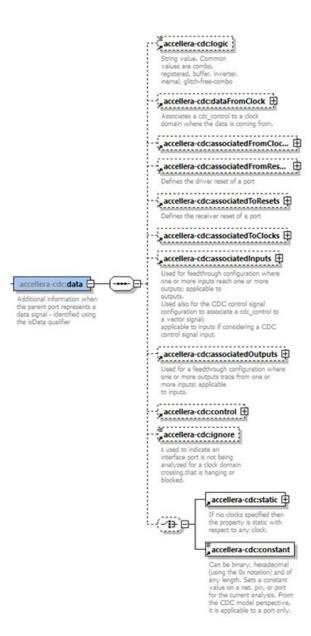

| 15                | 7.3                | Data port type—accellera-cdc:data                                       |     |

| 16                |                    | 7.3.1 IP-XACT code for accellera-cdc:data                               |     |

| 17                | 7.4                | Clock port type-accellera-cdc:clock                                     |     |

| 18                |                    | 7.4.1 IP-XACT code for accellera-cdc:clock                              |     |

| 19                |                    | 7.4.2 IP-XACT code for virtual accellera-cdc:clock                      |     |

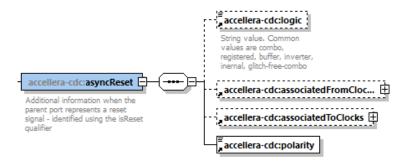

| 20                | 7.5                | Reset port type—accellera-cdc:asyncReset                                |     |

| 21                |                    | 7.5.1 IP-XACT code for accellera-cdc:asyncReset                         |     |

| 22                | 7.6                | Control port type—accellera-cdc:cdcControl and accellera-cdc:rdcControl |     |

| 23                |                    | 7.6.1 IP-XACT code for accellera-cdc:cdcControl                         |     |

| 24                | 7.7                | Control port type—accellera-cdc:componentCDCDef                         |     |

| 25                |                    | 7.7.1 IP-XACT code for accellera-cdc:componentCDCDef                    |     |

| 26                | 7.8                | Accellera CDC Vendor Extensions SCRs                                    | 103 |

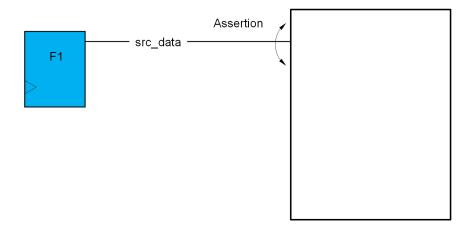

| 27 8.             | SVA                | A Requirements for black box CDC integrity verification                 | 104 |

| 28                | 8.1                | Overview                                                                | 104 |

| 29                | 8.2                | Sampling edge requirement                                               |     |

| 30                | 8.3                | Implementation headroom for a crossing                                  |     |

| 31                | 8.4                | Verification clock for a crossing                                       | 107 |

| 32 Ann<br>33 (inf | nex A<br>formative | e)                                                                      |     |

| 34 Bib            | liograph           | у                                                                       | 109 |

| 35 Ann            |                    |                                                                         |     |

|                   | ormative           | DC testcases                                                            | 110 |

# 1 List of figures

| 2 Figure 1—Circuit drawing template                                                                    |            |

|--------------------------------------------------------------------------------------------------------|------------|

| 3 Figure 2—Module attribute                                                                            |            |

| 4 Figure 3—Port attributes: name, direction, type                                                      | 33         |

| 5 Figure 4—Port attribute: associated from clocks                                                      | 35         |

| 6 Figure 5—Specifying a virtual clock                                                                  | 37         |

| 7 Figure 6—Port attribute: associated from reset and associated to reset                               |            |

| 8 Figure 7—Ignore: hanging                                                                             |            |

| 9 Figure 8—Ignore: blocked                                                                             |            |

| 10 Figure 9—Example showing the need to describe a pseudo static behavior on the data crossing domains |            |

| 11 Figure 10—Example of the DFT structure usage in a digital design                                    |            |

| 12 Figure 11—Example of a digital design explaining usage of the "constant" attribute                  |            |

| 13 Figure 12—Feedthrough logic                                                                         |            |

| 14 Figure 13—Internal synchronizer and internal combinatorial logic on paths through ports             |            |

| 15 Figure 14—Module mod0 with abstracted input ports                                                   |            |

| 16 Figure 15—Module mod0 with abstracted output ports                                                  |            |

| 17 Figure 16—Clock definition A                                                                        |            |

| 18 Figure 17—Clock definition B                                                                        |            |

| 19 Figure 18—Clock definition C                                                                        | . 64       |

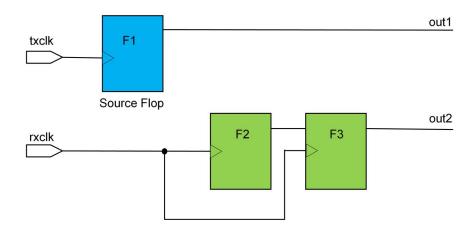

| 20 Figure 19—One clock domain                                                                          |            |

| 21 Figure 20—Two clock domains                                                                         |            |

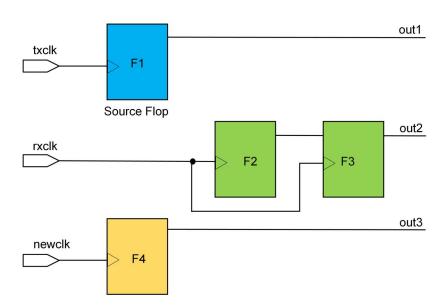

| 22 Figure 21—Three clock domains                                                                       |            |

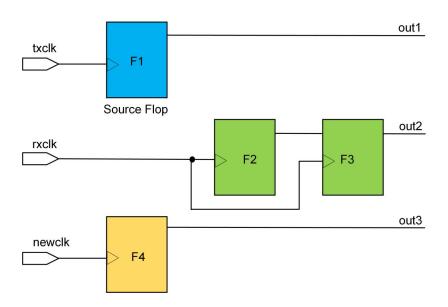

| 23 Figure 22—Two clock domains                                                                         |            |

| 24 Figure 23—Failure mode due to missing synchronizer                                                  |            |

| 25 Figure 24—Failure mode due to missing synchronized control                                          |            |

| 26 Figure 25—Failure mode due to missing reset synchronizer                                            |            |

| 27 Figure 26—Failure mode due to combo logic driving clock/reset                                       |            |

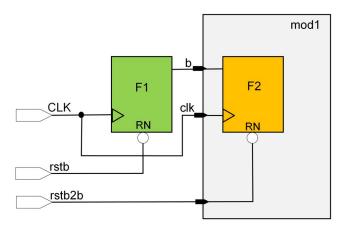

| 28 Figure 27—External rstb with internal synchronization logic                                         |            |

| 29 Figure 28—rstb2b of IP with associated reset                                                        |            |

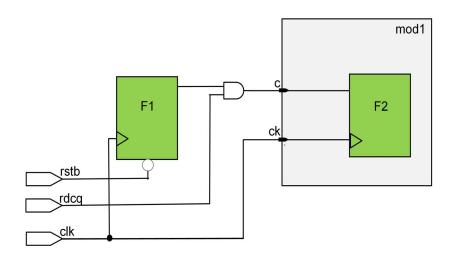

| 30 Figure 29—External rdcq on the data signal of the IP                                                |            |

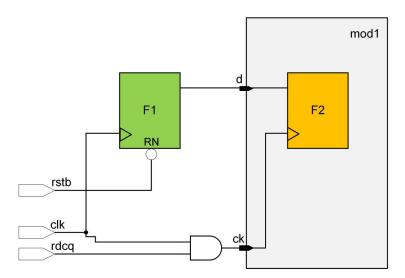

| 31 Figure 30—External rdcq on the clock signal of the IP                                               |            |

| 32 Figure 31—rstb of IP driven by multiple resets                                                      |            |

| 33 Figure 32—rstb of IP driven by multiple resets. Destination flop has no async reset pin             |            |

| 34 Figure 33—rstb of IP is controlling a flop that is driven by multiple resets                        |            |

| 354 Figure 34—rdcq is gating the interface clock                                                       | . 80       |

| 35 Figure 35—Internal rdcq                                                                             | . 02<br>00 |

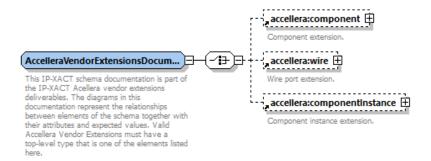

| 37 Figure 36—Schema for top-level elements                                                             |            |

| 37 Figure 30—Schema for top-level elements 38 Figure 37—Schema for accellera:wire                      |            |

| · ·                                                                                                    |            |

| 39 Figure 38—Schema for accellera-cdc:data                                                             |            |

| 40 Figure 39—Schema for accellera-cdc:clock                                                            |            |

| 42 Figure 41—Schema for accellera-cdc:asynckeset                                                       |            |

|                                                                                                        |            |

| 43 Figure 42—Schema for accellera-cdc:componentCDCDef                                                  |            |

| 44 Figure 43—Sampling edge requirement example                                                         |            |

| 45 Figure 44—Example of an untimed path at the clock domain boundary                                   |            |

| 46 Figure 45—Implementation headroom                                                                   |            |

| 47 Figure 46—Necessity of a faster clock                                                               | 108        |

# 1 List of tables

| 2 Table 1—CDC attributes: module domain              | 20 |

|------------------------------------------------------|----|

| 3 Table 3—CDC Attributes: port domain                | 21 |

| 4 Table 2—CDC attributes: parameter domain           |    |

| 5 Table 4—CDC Attributes: tool domain                | 27 |

| 6 Table 6—CDC Attributes: cdc_set_clock_group domain | 28 |

| 7 Table 5—CDC Attributes: design domain              | 28 |

| 8 Table 7—CDC Attributes: set reset group domain     | 29 |

| 9 Table 8—Parameter attributes                       | 30 |

| 10 Table 9—Parameter usage                           | 31 |

| 11 Table 10—Associated clocks usage for output ports |    |

| 12 Table 11—Associated clocks usage for input ports  | 36 |

| 13 Table 12—Supported async_reset attributes         | 47 |

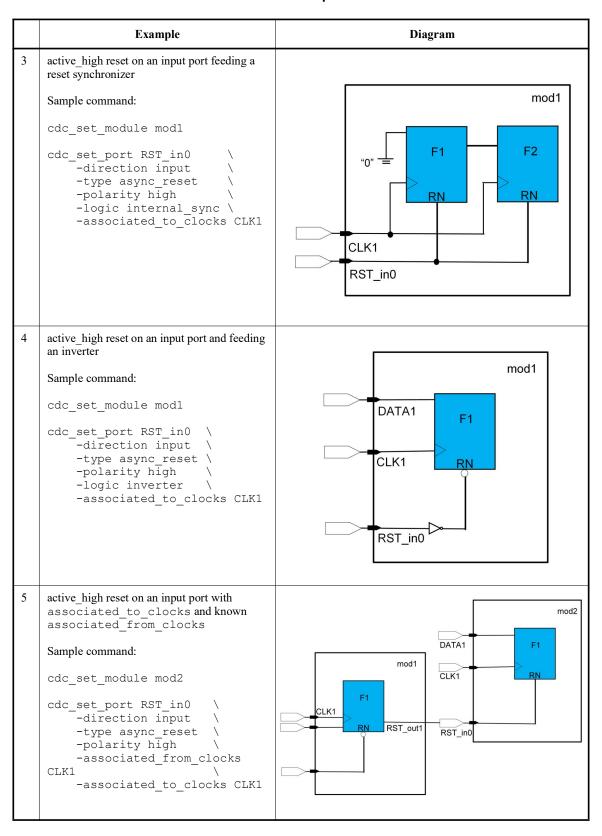

| 14 Table 13—Example cases                            | 49 |

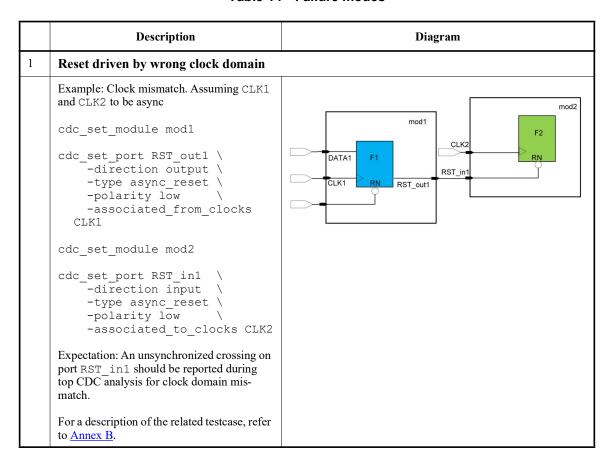

| 15 Table 14—Failure modes                            |    |

| 16 Table 15—CDC Port Attributes                      | 92 |

| 17 Table 16—CDC semantic consistency rules           |    |

| 18 Table 17—CDC and RDC testcases                    |    |

# <sup>2</sup>Clock Domain Crossing Standard 3 Version 0.5 Draft for Public Review

#### 41. Overview

5 This common CDC interface standard provides the following:

- 6 a) Every vendor's tool can translate its native format to and from the standard to maintain its IP.

- 5 b) Every IP provider can run its tool of choice to verify and produce collateral and generate the standard format for SOCs that use a different tool.

- 9 c) Every SOC can quickly and safely integrate either native collateral or translate from the standard collateral into their tool of choice to ensure time-to-market goals and quality.

11 A limited feasibility study was conducted on a subsystem with multiple IPs connected by Arm<sup>®</sup> AMBA<sup>®</sup> 12 interfaces across three vendor tools with limited support from the vendors. It showed that 99.5% of what 13 was identifiable in a flat run using any of the three vendor tools was also identifiable if the native abstraction 14 collateral was replaced with an XML representation and translated across the vendor tools. <sup>2</sup>

#### 15 **1.1 Scope**

16 The scope of work of the Clock Domain Crossing Standard is limited to:

- 17 a) Support tool-independent output collateral for CDC, RDC, and glitch structural analysis

- 18 b) Provide human-readable and machine-parsable attributes

- 19 c) Support customizable extensions (for example, to support complex user conditions)

- 20 d) Support hierarchical analysis

- 21 e) Support power-aware designs

- 22 f) Support multi-modal IP/SOC analysis

- 23 g) Support multi-instance IPs

- 24 h) Support parameterized IPs

- 25 i) Support multiple interface protocols (for example, AMBA, I2C, PCIe, UCIe, and so forth)

- 26 j) Provide extensibility to cover input collateral cases (for example, constraints, waivers, and so forth)

- to enable high-quality re-verification of an IP using alternate tools

- 28 k) Support assertions necessary to complement CDC, RDC, and glitch structural analyses

<sup>&</sup>lt;sup>1</sup>AMBA<sup>®</sup> is a registered trademark of Arm<sup>®</sup> Limited (or its subsidiaries) in the US and/or elsewhere

<sup>&</sup>lt;sup>2</sup>This feasibility study was only for CDC and did not include reset domain crossing (RDC) or glitch analysis.

- 1 l) Support other design styles (for example, FPGA and Analog) that follow similar standards

- 2 NOTE—The "interface protocols" item above is a way to ensure that multiple circuit styles (CDC crossing types) are 3 supported to maintain good integration quality.

- 4 Using standard interfaces that can be verified independently (for example, with VIP from independent sources) for the 5 integration of independently designed IPs limits the potential for bugs to be introduced. The above limitation does not 6 prevent innovation between sub-blocks, but instead discourages any complications from these innovations from being 7 spread across independent blocks that might not have been verified with the same tools. Using customizable extensions 8 of the format can address exceptions, but these extensions are not guaranteed by the standard.

#### 9 1.2 Purpose

10 The purpose of the Clock Domain Crossing standard is to:

- 11 a) Enable EDA vendors to develop CDC, RDC, and/or glitch analysis tools that meet the specification defined in this standard to generate tool-agnostic collateral

- 13 b) Enable IP companies to use their tool(s) of choice to perform CDC, RDC, and/or glitch analysis on 14 their IP and generate said collateral

- 15 c) Enable SOC companies to consume collateral generated by different IP vendors from their tool(s) of choice, into the SOC company's own tool(s) of choice

#### 17 1.3 Conventions used

18 The conventions used throughout the document are included here.

#### 19 1.3.1 Circuit drawing conventions

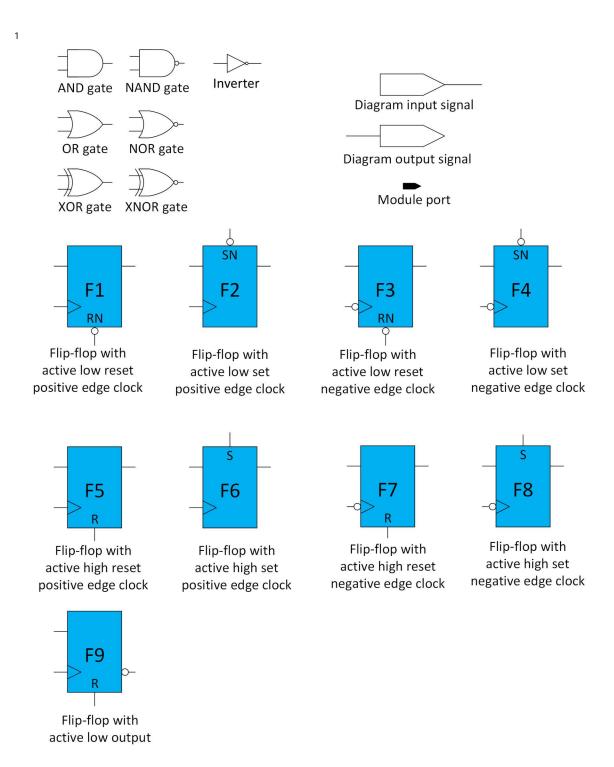

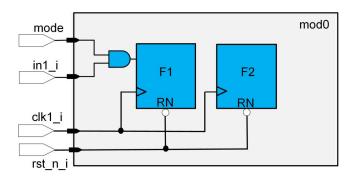

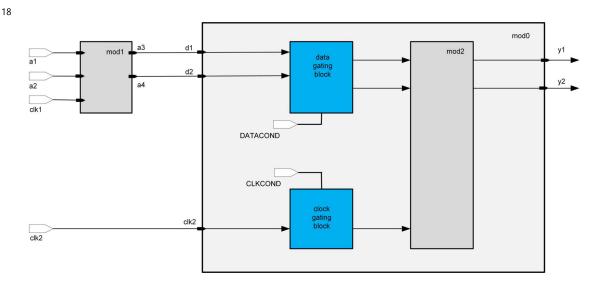

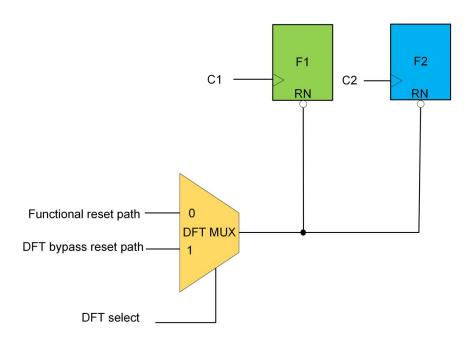

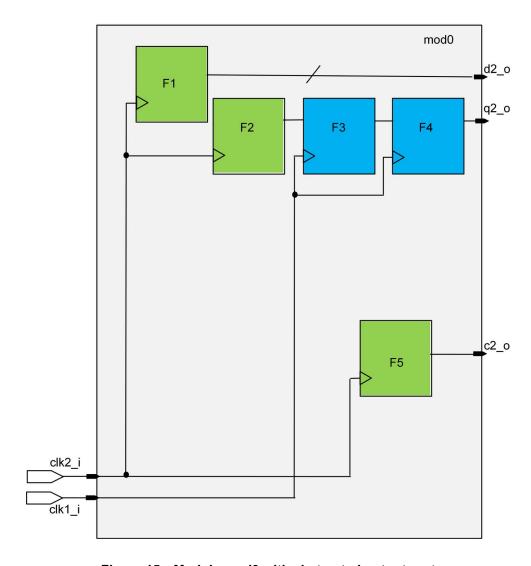

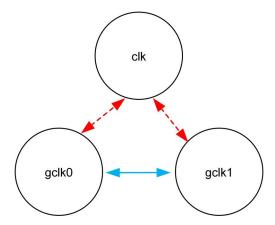

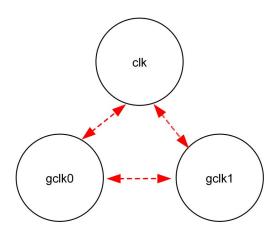

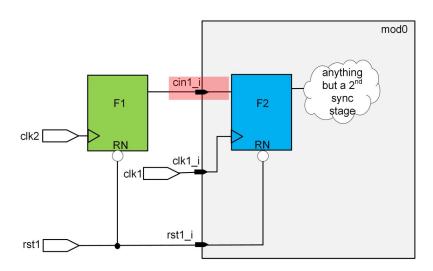

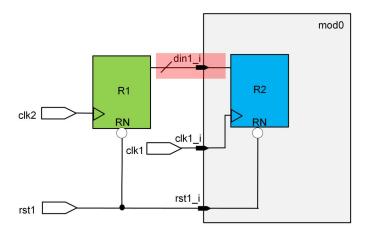

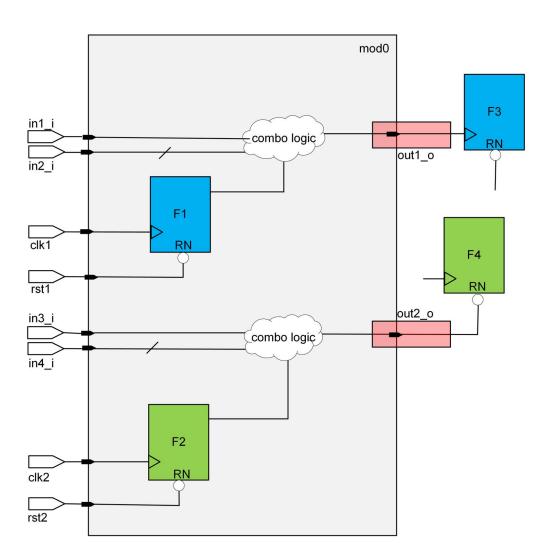

20 Use <u>Figure 1</u> as a guide to understanding the drawings in this LRM.

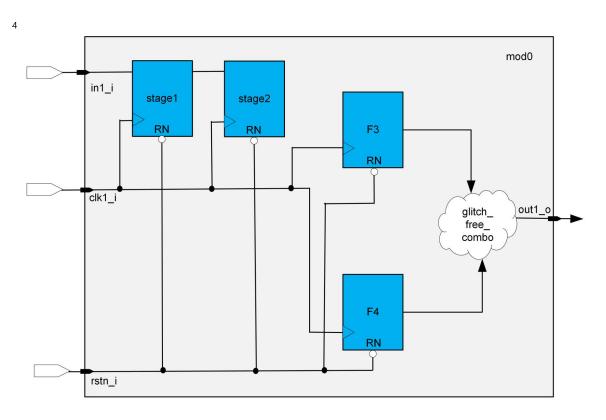

Figure 1—Circuit drawing template

3

2

4

#### 1 1.3.2 Word usage

- 2 The word *shall* indicates mandatory requirements strictly to be followed in order to conform to the standard 3 and from which no deviation is permitted (*shall* equals *is required to*).<sup>3,4</sup>

- 4 The word *should* indicates that among several possibilities one is recommended as particularly suitable, 5 without mentioning or excluding others; or that a certain course of action is preferred but not necessarily 6 required (*should* equals *is recommended that*).

- 7 The word *may* is used to indicate a course of action permissible within the limits of the standard (*may* equals 8 *is permitted to*).

- 9 The word *can* is used for statements of possibility and capability, whether material, physical, or causal (*can* 10 equals *is able to*).

#### 11 1.4 Use of color in this standard

- 12 This standard uses a minimal amount of color to enhance readability. The coloring is not essential and does 13 not affect the accuracy of this standard when viewed in pure black and white. The places where color is used 14 are the following:

- Cross references that are hyperlinked to other portions of this standard are shown in <u>underlined-blue</u> text (hyperlinking works when this standard is viewed interactively as a PDF file).

- 17 Illustrations. (The color can clarify, but it is not essential.)

#### 18 1.5 Contents of this standard

19 The organization of the remainder of this standard is as follows:

- 20 <u>Clause 2</u> provides references to other applicable standards that are assumed or required for this standard.

- Clause 3 defines terms and acronyms used throughout the different specifications contained in this

standard.

- Clause 4 lists CDC attributes along with their type, accepted values, whether they are mandatory,

and clarifying comments.

- Clause 5 lists RDC attributes and provides scenarios to describe support for an RDC interface at the

top level without resynthesizing the RTL of the IP.

- Clause 6 describes the CDC format that is based on the TCL language for CDC specification from an output collateral perspective.

- 30 <u>Clause 7</u> describes the CDC format that is based on the IP-XACT standard.

- 31 <u>Clause 8</u> describes SVA Requirements for black box CDC integrity verification.

- 32 Annex A provides an informative bibliography.

- Annex B provides a list of unit testcases for early testing by EDA vendors.

<sup>&</sup>lt;sup>3</sup> The use of the word *must* is deprecated and cannot be used when stating mandatory requirements; *must* is used only to describe unavoidable situations.

<sup>&</sup>lt;sup>4</sup> The use of will is deprecated and cannot be used when stating mandatory requirements; will is only used in statements of fact.

#### 12. References

2 The following referenced documents are indispensable for the application of this document. For dated 3 references, only the edition cited applies. For undated references, the latest edition of the referenced 4 document (including any amendments or corrigenda) applies.

5 IEEE Std 1685<sup>™</sup>-2022, IEEE Standard for IP-XACT, Standard Structure for Packaging, Integrating, and 6 Reusing IP within Tool Flows

7 IEEE Std 1800<sup>™</sup>-2017, IEEE Standard for SystemVerilog Unified Hardware Design, Specification and Ver-8 ification Language. <sup>5, 6</sup>

9

<sup>&</sup>lt;sup>5</sup>The IEEE standards or products referred to in this clause are trademarks of the Institute of Electrical and Electronics Engineers, Inc. <sup>6</sup>IEEE publications are available from the Institute of Electrical and Electronics Engineers, Inc., 445 Hoes Lane, Piscataway, NJ 08854, USA (https://standards.ieee.org/).

#### 13. Definitions, acronyms, and abbreviations

2 For the purposes of this document, the following terms and definitions apply. *The Authoritative Dictionary* 3 *of IEEE Standards Terms* [B1]<sup>7</sup> should be referenced for terms not defined in this clause.

#### 4 3.1 Definitions

5 **Accellera Vendor extensions**: Extensions to the IEEE Standard for IP-XACT that capture attributes related 6 to clock and reset to support the CDC Standard.

7 **component**: A physical and logical construction that relates inputs to outputs.

8 **glitch**: A transient pulse on a signal that is caused by a race between signals in its fan-in. This includes asyn-9 chronous data path (for example, combinational logic going into synchronizers or reconvergence of parallel 10 synchronizers) as well as clock and reset trees.

11 **port**: A connection on the interface of a SystemVerilog module or very high speed integrated circuit 12 (VHSIC) hardware description language (VHDL) entity.

13 **CDC control signal**: A signal that is either tool-inferred or user-specified as a clock domain crossing con-14 trol to a data path (scalar or vector) as it crosses clock domains.

#### 15 3.2 Acronyms and abbreviations

| CDC    |              | •          |

|--------|--------------|------------|

| 16 CDC | clock domain | crossing - |

|        |              |            |

17 Combo combinational logic

18 DFT design for test

19 EDA electronic design automation

20 HDL hardware description language

21 inout bidirectional port

22 internal sync internal synchronizer

23 IP intellectual property

24 IP-XACT IEEE standard describing an XML metadata schema for documenting IP; used

in the development, implementation, and verification of electronic systems

26 LRM language reference manual

27 MTBF mean time before failure

28 PWG proposed working group

29 RDC reset domain crossing

<sup>&</sup>lt;sup>7</sup>The numbers in brackets correspond to those of the bibliography in <u>Annex A</u>.

| 1 QoR          | quality of results                                                                                                                                                                                         |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 RTL          | register transfer level                                                                                                                                                                                    |

| 3 SDC          | Synopsys Design Constraints                                                                                                                                                                                |

| 4 SOC          | system on chip or products that consist of various IPs and glue-logic                                                                                                                                      |

| 5 SVA          | SystemVerilog Assertions                                                                                                                                                                                   |

| 6 STA          | static timing analysis                                                                                                                                                                                     |

| 7 SWG          | sub-workgroup                                                                                                                                                                                              |

| 8 TCL          | Tool Command Language                                                                                                                                                                                      |

| 9 VIP          | validation IP or test environment used to test aspects of an IP                                                                                                                                            |

| 10 WG          | working group                                                                                                                                                                                              |

| 11 XML         | eXtensible Markup Language                                                                                                                                                                                 |

| 12<br>13<br>14 | NOTE—CDC WG refers to CDC-, RDC-, and glitch-related (asynchronous data crossing) checks necessary for correct functionality of clock, reset, and data glitch (associated with clock and reset crossings). |

| 15             |                                                                                                                                                                                                            |

#### 14. CDC Attributes

2 The CDC attributes are expressed in case-sensitive TCL for the CDC tool-level format, but you have the 3 option to translate this Tcl to IP-XACT for packaging the IP (see <u>Clause 6</u> and <u>Clause 7</u>).

4 This version of the LRM includes case-sensitive TCL commands to support EDA vendors with tool 5 development. (Also see <u>Clause 6</u>.) The case-sensitive TCL captures data required from input, output, and 6 verification collateral in a human-readable and machine-parsable format to provide accurate CDC, RDC, 7 and glitch structural analysis by any EDA tool. The CDC attributes format supports customizable extensions 8 for complex user conditions. In addition, these attributes are applicable to other design styles (e.g., FPGA 9 and Analog) that follow similar standards.

10 The CDC attributes facilitate a correct CDC and RDC integration of blocks in an encompassing design and 11 address a specific set of known industry standard interfaces. The CDC standard identifies both the CDC and 12 RDC schemes the attributes support and those schemes the defined set of attributes is not guaranteed to 13 support.

14 Each table below is associated with an attribute domain (i.e., module, parameter, port, and so forth), and 15 within each table, the applicable attributes are listed along with their type, accepted values, whether they are 16 mandatory, and clarifying comments. (Also see <u>Clause 5</u> for additional information about RDC attributes.) 17 Use the drawings and accompanying case-sensitive TCL examples in the sections following the tables to 18 understand clock relationships and various crossings and failure modes. These sections include the 19 following:

- 20 a) Module attribute

- 21 b) Parameter attributes

- 22 c) Port attributes

- 23 d) async reset

- e) <u>Modeling abstracted blocks</u>

- 25 f) Clock definitions

- 26 g) Clock relationships

- 27 h) Failure modes

28 NOTE—Support for an -update or -add argument will be considered in the future for incrementally building com-29 mands. In the case of conflicting commands, the final command is recognized.

30 Table 1 lists details of the module domain attribute: name.

Table 1—CDC attributes: module domain

| Domain | Attribute | Туре   | Values        | Conditions of usage | Comments             |

|--------|-----------|--------|---------------|---------------------|----------------------|

| module | name      | string | {module name} | Mandatory           | See also: <u>4.1</u> |

31

32 <u>Table 2</u> lists details of the parameter domain attributes.

33

Table 2—CDC attributes: parameter domain

| Domain    | Attribute | Туре        | Values                                                                                                                       | Conditions<br>of usage | Comments             |

|-----------|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|

| parameter | name      | string      | {parameter name}                                                                                                             | Mandatory              | See also: <u>4.2</u> |

| parameter | value     | range-list  | {values}                                                                                                                     | Optional               | See also: <u>4.2</u> |

| parameter | type      | defined set | {string, Boolean*, number (hex, decimal, oct, binary)}  * Boolean values 0/1 and true/false (case independent) are accepted. | Optional               | See also: <u>4.2</u> |

| parameter | ignore    | Boolean     | {0 or 1,<br>true or false}<br>(case independent)                                                                             | Optional               | See also: 4.2        |

1

2

3 <u>Table 3</u> lists details of the port domain attributes.

Table 3—CDC Attributes: port domain

| Domain | Attribute | Туре           | Values                                                                                            | Conditions of usage                               | Comments                                                                                                                                                                                                             |

|--------|-----------|----------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| port   | name      | string         | {port name}                                                                                       | Mandatory                                         | See also: <u>4.3.1</u>                                                                                                                                                                                               |

| port   | direction | defined<br>set | {input,<br>output,<br>inout}                                                                      | Mandatory                                         | See also: <u>4.3.1</u>                                                                                                                                                                                               |

| port   | type      | defined<br>set | {data, clock,<br>virtual_clock,<br>async_reset,<br>cdc_control,<br>rdc_control,<br>virtual_reset} | Mandatory  Mandatory applies to async reset only. | For async resets, type is async_resets, for sync resets, type is data.  Type virtual_clock defines a virtual clock port that does not match an actual port in the module.  See also: 4.3.1, 4.3.4, 4.4, and Clause 5 |

Table 3—CDC Attributes: port domain (continued)

| Domain                                                                                           | Attribute                                                                                                                                                                                                                                     | Туре                                              | Values                                                       | Conditions of usage                                                                                 | Comments                                                                                                            |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| port                                                                                             | logic                                                                                                                                                                                                                                         | defined<br>set                                    | {combo,<br>inverter,<br>glitch_free_combo,<br>internal_sync} | Optional                                                                                            | Without this attri-<br>bute, the assump-<br>tion is that the port<br>directly reaches a<br>sequential ele-<br>ment. |

|                                                                                                  |                                                                                                                                                                                                                                               |                                                   |                                                              |                                                                                                     | See also: <u>4.3.10</u>                                                                                             |

| port                                                                                             | cdc_data_from_clock                                                                                                                                                                                                                           | string                                            | {clock name}                                                 | Conditional  Mandatory for ports of type cde_control.                                               | Supports only one clock.  See the definition below.  See also: 4.5, Figure 15                                       |

| Definition:                                                                                      | Associates a cdc_control to a                                                                                                                                                                                                                 | clock domain                                      | where the data is coming                                     | ng from.                                                                                            | I                                                                                                                   |

| -dil<br>-typ<br>-loo<br>-ass<br>-cdo<br>-ass<br>cdc_set_<br>-dil<br>-typ<br>-ass<br>-cdo<br>-ass | _port sync_valid rection input pe cdc_control gic internal_sync sociated_from_clocks c_data_from_clock VC sociated_to_clocks r: _port sync_valid rection input pe cdc_control sociated_from_clocks c_data_from_clock VC sociated_to_clocks r: | LK_tx_clock x_clock  rx_clock LK_tx_clock x_clock | ck<br>ck                                                     |                                                                                                     |                                                                                                                     |

| port                                                                                             | associated_from_clocks                                                                                                                                                                                                                        | space-<br>separated<br>list                       | {clock-names}                                                | Conditional  This attribute is mandatory for an input port unless the input port is not received by | See also: <u>4.3.2</u> and <u>4.5</u>                                                                               |

any clock domain.

#### Table 3—CDC Attributes: port domain (continued)

| Domain | Attribute            | Туре                        | Values        | Conditions of usage                                                                                                        | Comments                                               |

|--------|----------------------|-----------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| port   | associated_to_clocks | space-<br>separated<br>list | {clock-names} | Conditional  This attribute is mandatory for an output port unless the output port is not generated from any clock domain. | For default values, see 4.3.3.  See also 4.5 and 5.1.4 |

| port   | associated_inputs    | space-<br>separated<br>list | {ports}       | Optional                                                                                                                   | See the definition below.  See also: 4.5               |

Definition: Used for feedthrough configuration where one or more inputs reach one or more outputs; applicable to outputs.

Used also for the CDC control signal configuration to associate a cdc\_control to a vector signal; applicable to inputs if considering a CDC control signal input.

| port | associated_outputs | space-<br>separated | {ports} | Optional | See the definition below. |

|------|--------------------|---------------------|---------|----------|---------------------------|

|      |                    | list                |         |          | ociow.                    |

|      |                    | 1150                |         |          | See also: <u>4.3.9</u>    |

Definition: Used for a feedthrough configuration where one or more outputs trace from one or more inputs; applicable to inputs.

The cdc control signal configuration might be useful.

| port | cdc_control       | space-<br>separated<br>list | {associated-ports} | Optional    | See also: <u>4.5</u>      |

|------|-------------------|-----------------------------|--------------------|-------------|---------------------------|

| port | cdc_control_setup | integer                     | value              | Conditional | See the definition below. |

|      |                   |                             |                    |             | See also: <u>4.5</u>      |

Definition: Sets a constant value on a port with the cdc\_control attribute to define the setup margin between the cdc\_control port and its associated\_inputs data port. The value of this attribute is the number of destination clock cycles the associated\_inputs data port must be stable before the cdc\_control port enables the data crossing. If the value is 3, associated\_inputs data port must be stable for 3 destination clock cycles before cdc\_control enables data crossing. If the value is -2, associated\_inputs data port can toggle at max up to 2 destination clock cycles after cdc\_control enables data crossing.

| port | cdc_control_hold | integer | value | Conditional | See the definition below. |

|------|------------------|---------|-------|-------------|---------------------------|

|      |                  |         |       |             | See also: <u>4.5</u>      |

Definition: Sets a constant value on a port with the cdc\_control attribute to define the hold margin between the cdc\_control port and its associated\_inputs data port. The value of this attribute is the number of destination clock cycles the associated\_inputs data port must be stable after the cdc\_control port disables the data crossing. If the value is 3, associated\_inputs data port must be stable for 3 destination clock cycles after cdc\_control disables data crossing. If the value is -2, associated\_inputs data port can change at most 2 destination clock cycles before cdc\_control disables data crossing.

Table 3—CDC Attributes: port domain (continued)

| Domain | Attribute     | Туре           | Values        | Conditions of usage                                                                                                                                                                                                                                                      | Comments                                 |

|--------|---------------|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| port   | sampling_edge | defined<br>set | {pos,<br>neg} | Conditional  This attribute is mandatory if the IP provider requires minimum pulse width assertion at a single bit input that is received by a synchronizer in the IP. In such cases, the input signal should be also described by the attribute "-logic internal_sync". | See the definition below.  See also: 4.5 |

Definition: Paired with cdc\_control port type or a single-bit data port type that requires synchronization to define the sampling edge of the first receiving flop of the destination domain. The string "pos" is attributed to the positive edge of the destination clock sampling the source data. The string "neg" is attributed to the negative edge of the destination clock sampling the source data.

| port | polarity   | defined<br>set              | {high,<br>low,<br>low_high}            | Conditional  This attribute is mandatory for async reset, cdccontrol, and rdc_control; otherwise, it is optional. | For cdc_control<br>and rdc_control,<br>"low_high" is not<br>allowed. |

|------|------------|-----------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| port | ignore     | defined<br>set              | {blocked,<br>hanging}                  | Optional                                                                                                          | See also: <u>4.3.6</u>                                               |

| port | cdc_static | space-<br>separated<br>list | {clock-names}                          | Optional                                                                                                          | See also: 4.3.7                                                      |

| port | constant   | space-<br>separated<br>list | {binary,<br>hex,<br>and of any length} | Optional                                                                                                          | See the definition below.  See also: 4.3.8                           |

Definition: Sets a constant value on a net, pin, or port for the current analysis. From the CDC model perspective, it is applicable to a port only.

It is relevant for all signal types (data, control, etc.).

### Table 3—CDC Attributes: port domain (continued)

| Domain                      | Attribute                                                                                                                  | Туре                             | Values                                             | Conditions of usage                 | Comments                                                                                                                                                                 |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| port                        | gray_coded                                                                                                                 | Boolean                          | {0 or 1,<br>true or false}                         | Optional                            | See the definition below.                                                                                                                                                |

|                             |                                                                                                                            |                                  | Default: 0 or false (case independent)             |                                     | Deferred to LRM v0.5                                                                                                                                                     |

| changing so<br>If a user ha | Implies mutually exclusivene equentially). gray_coded ports a specified these on input port any validation other than asse | s are used to eles, then an asse | liminate convergence an ertion is generated to che | d glitch violation eck for non-gray | s inside an IP.                                                                                                                                                          |

| port                        | clock_period                                                                                                               | string                           | {clock period}                                     | Conditional                         | See definition below.                                                                                                                                                    |

|                             | od is used to identify relative c<br>for detecting if violations coul                                                      |                                  |                                                    |                                     | nere assertions could                                                                                                                                                    |

| port                        | associated_from_reset                                                                                                      | space-<br>separated<br>list      | {reset-names}                                      | Optional                            | Defines the driver reset of a port  See also: 4.3.5                                                                                                                      |

| port                        | associated_to_reset                                                                                                        | space-<br>separated<br>list      | {reset-names}                                      | Optional                            | Defines the receiver reset of a port                                                                                                                                     |

|                             |                                                                                                                            |                                  |                                                    |                                     | See also: <u>4.3.5</u>                                                                                                                                                   |

| port                        | rdc_control                                                                                                                | space-<br>separated<br>list      | {associated-port}                                  | Conditional                         | See also: <u>5.2</u>                                                                                                                                                     |

| port                        | rdc_data_from_reset                                                                                                        | space-<br>separated<br>list      | {reset-names}                                      | Optional                            | Used with rdc_control.  Defines the source reset of the RDC; i.e., the start point's reset.  This is the source reset being blocked by -rdc_control.  See also: Clause 5 |

| port                        | rdc_data_to_reset                                                                                                          | space-<br>separated<br>list      | {reset-names}                                      | Optional                            | Used with rdc_control.  Defines the destination reset of the RDC; i.e., the end point's reset.  See also: Clause 5                                                       |

Table 3—CDC Attributes: port domain (continued)

| Domain | Attribute               | Туре                        | Values                 | Conditions of usage | Comments                                                                                                                                                            |

|--------|-------------------------|-----------------------------|------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

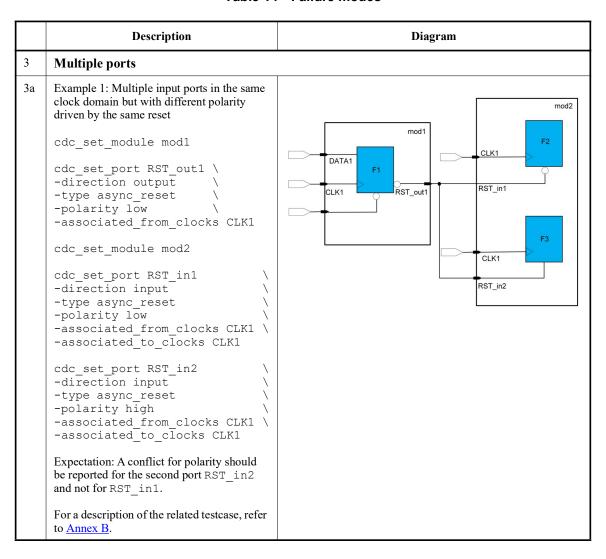

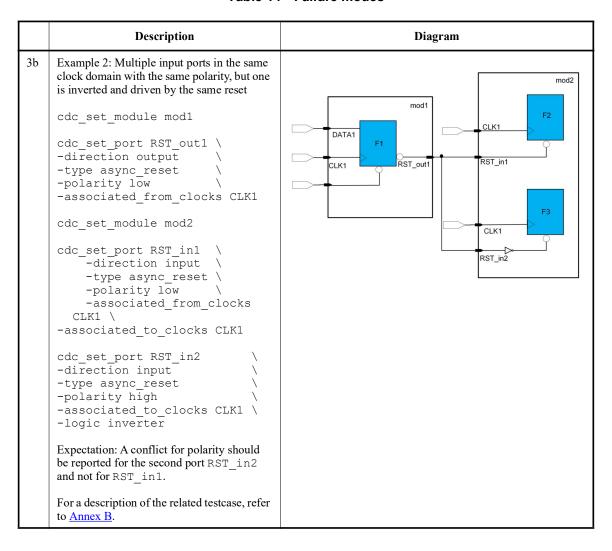

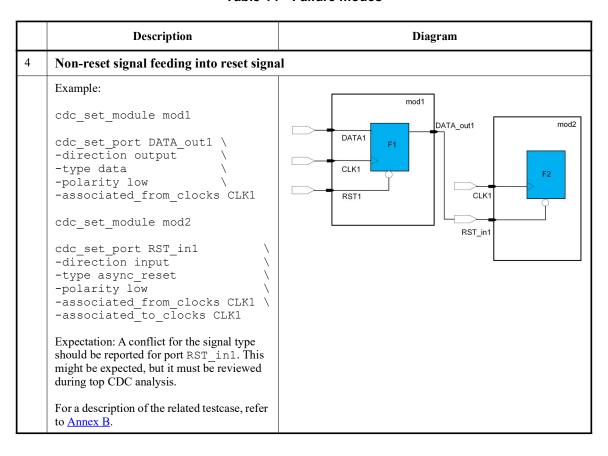

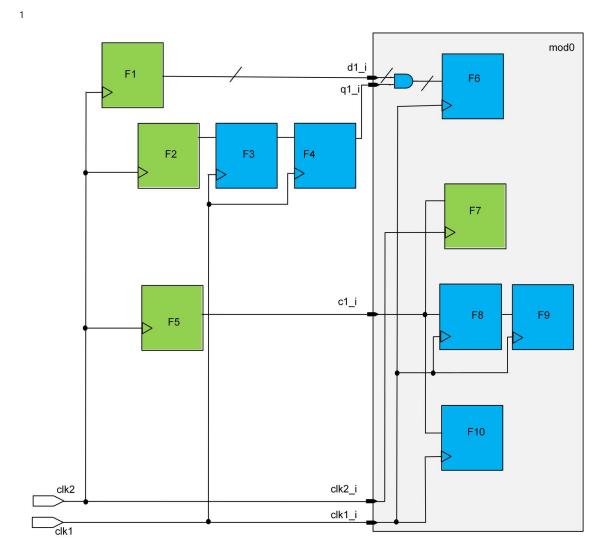

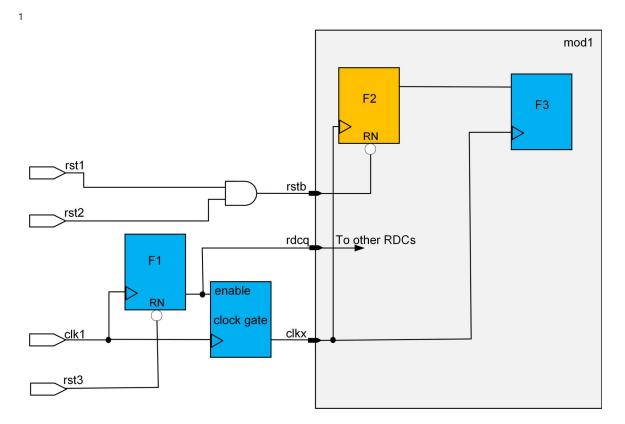

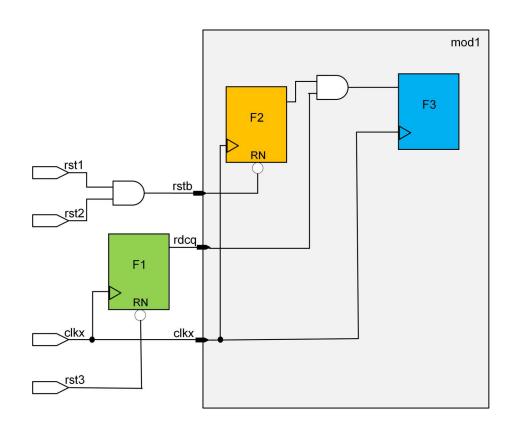

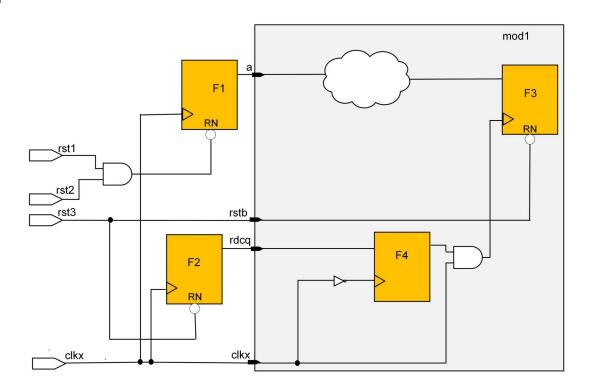

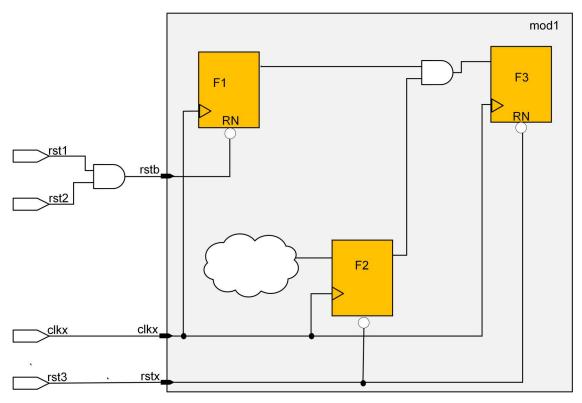

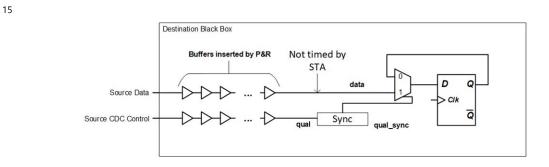

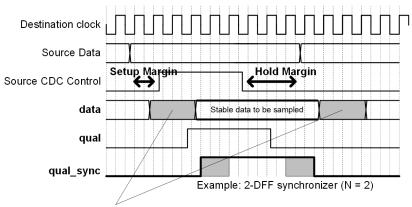

| port   | rdc_data_to_clock       | space-<br>separated<br>list | {clock-names}          | Optional            | Used with rdc_control.  Defines the destination clock of the RDC end point's clock.  This is the destination clock being gated by -rdc_control.  See also: Clause 5 |