# Universal Verification Methodology for Mixed-Signal Standard (UVM-MS) Version 1.0

January 2025

**Abstract:** The Universal Verification Methodology for Mixed-Signal (UVM-MS) is a comprehensive and unified analog/mixed-signal verification methodology based on the Universal Verification Methodology Standard (UVM, IEEE Std 1800.2) that improves analog/mixed-signal (AMS) and digital/mixed-signal (DMS) verification of integrated circuits and systems. This standard defines a framework that enables the creation of analog/mixed-signal verification components and test benches by extending digital-centric UVM classes and facilitating interaction between class-based and structural environments. The objective is to standardize methods for driving and monitoring mixed-signal nets within UVM. The reuse of proven verification components will in turn increase the productivity of verification teams and improve overall quality. The overall UVM-MS methodology is explored with supporting examples and use cases.

**Keywords:** agent, AMS, analog, class, DMS, interface, messaging, mixed-signal, proxy, RNM, SystemVerilog, Universal Verification Methodology, UVM, UVM-MS, verification

#### **Notices**

Accellera Systems Initiative (Accellera) Standards documents are developed within Accellera and the Technical Committee of Accellera. Accellera develops its standards through a consensus development process, approved by its members and board of directors, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are members of Accellera and serve without compensation. While Accellera administers the process and establishes rules to promote fairness in the consensus development process, Accellera does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards.

Use of an Accellera Standard is wholly voluntary. Accellera disclaims liability for any personal injury, property or other damage, of any nature whatsoever, whether special, indirect, consequential, or compensatory, directly or indirectly resulting from the publication, use of, or reliance upon this, or any other Accellera Standard document.

Accellera does not warrant or represent the accuracy or content of the material contained herein, and expressly disclaims any express or implied warranty, including any implied warranty of merchantability or suitability for a specific purpose, or that the use of the material contained herein is free from patent infringement. Accellera Standards documents are supplied "AS IS."

The existence of an Accellera Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of an Accellera Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change due to developments in the state of the art and comments received from users of the standard. Every Accellera Standard is subjected to review periodically for revision and update. Users are cautioned to check to determine that they have the latest edition of any Accellera Standard.

In publishing and making this document available, Accellera is not suggesting or rendering professional or other services for, or on behalf of, any person or entity. Nor is Accellera undertaking to perform any duty owed by any other person or entity to another. Any person utilizing this, and any other Accellera Standards document, should rely upon the advice of a competent professional in determining the exercise of reasonable care in any given circumstances.

**Interpretations**: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of Accellera, Accellera will initiate action to prepare appropriate responses. Since Accellera Standards represent a consensus of concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason, Accellera and the members of its Technical Committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments for revision of Accellera Standards are welcome from any interested party, regardless of membership affiliation with Accellera. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Comments on standards and requests for interpretations should be addressed to:

Accellera Systems Initiative 8698 Elk Grove Blvd Suite 1, #114 Elk Grove, CA 95624 USA

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. Accellera shall not be responsible for identifying patents for which a license may be required by an Accellera standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

Accellera is the sole entity that may authorize the use of Accellera-owned certification marks and/or trademarks to indicate compliance with the materials set forth herein.

Authorization to photocopy portions of any individual standard for internal or personal use must be granted by Accellera, provided that permission is obtained from, and any required fee is paid to Accellera. To arrange for authorization please contact Lynn Garibaldi, Accellera Systems Initiative, 8698 Elk Grove Blvd Suite 1, #114, Elk Grove, CA 95624, phone (916) 670-1056, e-mail lynn@accellera.org. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained from Accellera.

Suggestions for improvements to the UVM-MS Methodology are welcome. They should be posted to the UVM-MS Community Forum at:

https://forums.accellera.org/forum/60-uvm-mixed-signal/

The current Working Group web page is:

http://www.accellera.org/activities/working-groups/uvm-ms

## **Participants**

The UVM Mixed-Signal Working Group (UVM-MS WG) is entity-based. At the time this standard was completed, the UVM-MS Working Group had the following active participants:

Tom Fitzpatrick, Siemens EDA, Chair Tim Pylant, Cadence Design Systems, Vice Chair Shalom Bresticker, Retired, Technical Editor

Cadence Design Systems, Inc.: Chandrashekar Chetput, Abhijit Madhu Kumar

**Intel Corporation:** Boon Chong Ang, J. David Rosen **NXP Semiconductors:** Joachim Geishauser, Manish Patel

Qualcomm Incorporated: Bob Pau

Renesas Electronics Corp.: Peter Grove, Steven Holloway

Siemens EDA: Mina Louis Zaki

Synopsys, Inc.: Tushar Pandey, Msehli Slim, Weiming Zhu

At the time of standardization, the UVM-MS WG had the following eligible voters:

Cadence Design Systems, Inc. Renesas Electronics Corp.

Intel Corporation Siemens EDA

NXP Semiconductors Synopsys, Inc.

**Qualcomm Incorporated**

1

# **Contents**

| 1. Overview                                           | 8  |

|-------------------------------------------------------|----|

| 1.1 Scope                                             | 8  |

| 1.2 Purpose                                           | 8  |

| 1.3 Approach                                          | 8  |

| 1.4 Word usage                                        | 9  |

| 2. Normative references.                              | 10 |

| 2. Normative references                               | 10 |

| 3. Definitions, acronyms and abbreviations            |    |

| 3.1 Definitions                                       |    |

| 3.2 Other acronyms and abbreviations                  | 11 |

| 4. UVM-MS architecture                                | 11 |

| 4.1 Introduction                                      |    |

| 4.2 MS bridge                                         |    |

| 4.2.1 MS proxy                                        |    |

| 4.2.2 SV interface.                                   |    |

| 4.2.3 Bridge core                                     |    |

| 4.3 UVM-MS agent                                      |    |

| 4.3.1 UVM-MS driver                                   |    |

| 4.3.2 UVM-MS monitor                                  |    |

| 4.3.3 UVM-MS sequence item.                           |    |

| 4.4 UVM-MS scoreboard and coverage                    |    |

| 4.5 UVM-MS testbench                                  |    |

|                                                       |    |

| 5. Bridge configuration                               | 19 |

| 6. Bridge core communication                          | 23 |

| 6.1 AMS communication                                 |    |

| 6.1.1 Event generation from analog signals            |    |

| 6.1.2 Quantized continuously monitored analog signals |    |

| 6.1.3 Event-driven queries of analog values           |    |

| 6.1.4 Push analog control                             |    |

| 6.1.5 Push analog control with handshake (push-sync)  |    |

| 6.1.6 Pull analog value                               | 28 |

| 6.2 DMS communication                                 | 28 |

| 6.2.1 Event generation from analog signals            | 29 |

| 6.2.2 Quantized continuously monitored analog signals | 29 |

| 6.2.3 Event-driven queries of analog values           |    |

| 6.2.4 Push analog control                             | 30 |

| 6.2.5 Push analog control with handshake (push-sync)  | 30 |

| 6.2.6 Pull analog value                               | 31 |

| 7. Messaging                                          | 21 |

|                                                       |    |

| 7.1 General                                           |    |

| 7.2.1 UVM messaging from an AMS bridge core           |    |

| 7.2.1 UVM messaging from a DMS bridge core            |    |

| 7.2.2 O VIVI messaging nom a Divis oringe core        |    |

| 8. Testbench                                          | 33 |

|                                                       |    |

| 9. (informative) Verilog-AMS circuit initialization.  | 33 |

## Universal Verification Methodology for Mixed-Signal Standard – January 2025

| 9.1 General                                            | 33 |

|--------------------------------------------------------|----|

| 9.2 UVM phases                                         | 32 |

| 10. Known limitations                                  | 35 |

| 10.1 Inout ports on the SystemVerilog interface        | 35 |

| 10.2 Unpacked array ports on DUT                       |    |

| (normative) UVM-MS package and include files           | 36 |

| A.1 uvm_ms_pkg.sv                                      |    |

| A.2 uvm ms includes.svh                                | 36 |

| A.3 uvm_ms_includes.vamsh                              | 37 |

| Annex A (informative) Example: migrating UVM to UVM-MS | 39 |

| B.1 Overview                                           | 39 |

| B.2 Creating the bridge module                         | 41 |

| B.3 Extending the driver and monitor classes           | 42 |

| Annex B B.4 Extending the sequence item class          | 45 |

| B.5 Extending the scoreboard class                     |    |

| B.6 Changes to testbench class                         |    |

| B.7 Changes to top-level module                        |    |

| (informative) Bibliography                             | 53 |

Annex C

#### 1. Overview

#### 1.1 Scope

The Universal Verification Methodology for Mixed-Signal Standard (UVM-MS) is a comprehensive and unified analog/mixed-signal verification methodology based on the Universal Verification Methodology (UVM, IEEE Std 1800.2<sup>TM</sup>) that improves analog/mixed-signal (AMS) and digital/mixed-signal (DMS) verification of integrated circuits and systems. This framework enables the creation of mixed-signal verification components and test benches by extending digital-centric UVM classes and facilitating interaction between class-based and structural environments. The objective is to standardize methods for driving and monitoring mixed-signal nets within UVM. The reuse of proven verification components will in turn increase the productivity of verification teams and improve overall quality.

The overall UVM-MS methodology is explored with supporting examples and use cases.

#### 1.2 Purpose

Recent trends in integrated circuit and system design have seen an increase in the level of interaction between digital logic and analog circuitry. As the level of interaction has increased, the overall level of complexity of SoCs (Systems on Chips) has also increased rapidly. Functional digital verification has evolved over time to meet the demands of increased complexity, enjoying the benefits of automated flows, metric-driven verification, and other well-defined and understood methodologies. Analog functional verification methodologies have not developed at the same pace. Bridging the gap between the analog and digital methodologies is critical to ensuring robust verification of mixed-signal integrated circuits. Verifying mixed-signal designs is challenging and requires a solution capable of dealing with the increased complexity and ever-reducing time-to-market requirements.

UVM-MS extends the use of UVM components and extensions thereof into the physical layer, enabling mixed-signal verification. The methodology presents a solution for the following requirements:

- Define analog behavior based on a set of parameters defined in a **uvm\_sequence\_item** and generate that analog signal using a *mixed-signal bridge* module;

- Measure the properties of the analog signal, return them to a UVM monitor, package those properties into a sequence item, and potentially collect coverage and/or check correctness;

- Set controls for pre-run configurations via constraints.

#### 1.3 Approach

Mixed-signal simulations contain signals in both analog and digital domains. These signals may need to be driven or monitored by UVM components. However, UVM components can only directly interact with these signals digitally. While the conversion to analog signals could be handled using Verilog-AMS *connect modules*, for example, the analog signals can more naturally, consistently, and accurately be modeled in the analog domain. At the same time, mixed-signal simulations may be performed with different signal representations, so it is desirable to have a uniform interface between the signal (regardless of domain) and the UVM component with which it interacts. In order to provide this uniform interface, a UVM-MS testbench needs to include a *bridge* between a UVM-accessible API and the actual SystemVerilog, Verilog-AMS, or SPICE connection to the signals.

UVM-MS is an extension to UVM, so that users can build on their existing UVM infrastructure as much as possible when they need to incorporate mixed-signal designs into their system. A typical UVM testbench consists of a set of classes, each derived from the **uvm\_component** base type, that are instantiated and connected to allow stimulus and response checking between the testbench and the DUT (Device Under Test). Each DUT interface is connected via a SystemVerilog *virtual interface* to a **uvm\_agent**, which includes the following protocol-specific components to interact with the DUT:

- The uvm sequencer arbitrates between uvm sequences and sends a uvm sequence item to the uvm driver.

- The *uvm\_driver* gets the *uvm\_sequence\_item* from the *uvm\_sequencer*, and uses the information contained therein to communicate with the DUT via the virtual interface. The *uvm\_driver* may also receive responses from the DUT and pass them back via the sequencer to the originating *uvm\_sequence*.

- The *uvm\_monitor* recognizes behaviors on the virtual interface and encapsulates these into *uvm\_sequence\_item* objects to communicate them to other components in the environment, possibly including coverage collectors and/or scoreboards.

UVM-MS takes advantage of the existing UVM architecture and extends it to allow interactions between the UVM agent and the mixed-signal DUT. As outlined below, UVM-MS defines a separate *MS Bridge* module that connects to the virtual interface to interact directly with the UVM driver and monitor on one side and to the mixed-signal DUT on the other.

The MS Bridge Core implements the physical connection functions required by the UVM agent driver and monitor as well as data type conversions between the agent and the DUT I/O (Input/Output). Thus, UVM-MS eliminates any requirements for Verilog-AMS connect modules within the MS Bridge. The core is written in the language that allows best possible representation of the DUT I/O net abstraction. The MS Bridge also includes an MS Proxy class object (a handle to which is passed to the UVM driver and monitor) to provide an application programming interface (API) to allow the driver to call proxy class methods that control the bridge core.

Updating an existing digital-only UVM environment can then be accomplished by defining a new driver class, extended from the existing UVM driver, that includes a pointer to the proxy class object and possibly utilizes a new sequence item extended from the digital-only sequence item. The UVM factory allows for these new classes to be used without having to modify the existing UVM environment code. Similarly, the UVM test could replace the original sequence with a new sequence that uses the new sequence item to define a verification scenario targeted at the mixed-signal DUT. The rest of the UVM environment could be reused with minimal, if any, modifications.

If starting with an analog/mixed-signal DUT, the UVM environment can be defined from the beginning to rely on the *MS Bridge* and the proxy class to interact with the DUT. All other aspects of the environment, including the UVM test, would follow existing UVM guidelines, thus providing for a modular, reusable, constraint-driven verification environment similar to what digital verification engineers have used for many years.

## 1.4 Word usage

The word *shall* indicates mandatory requirements strictly to be followed in order to conform to the standard and from which no deviation is permitted (*shall* equals *is required to*).  $^{1,2}$

The word *should* indicates that among several possibilities one is recommended as particularly suitable, without mentioning or excluding others; or that a certain course of action is preferred but not necessarily required (*should* equals *is recommended that*).

The word may is used to indicate a course of action permissible within the limits of the standard (may equals is permitted to).

The word *can* is used for statements of possibility and capability, whether material, physical, or causal (*can* equals *is* able to).

-

<sup>&</sup>lt;sup>1</sup> The use of the word *must* is deprecated and cannot be used when stating mandatory requirements; *must* is used only to describe unavoidable situations.

<sup>&</sup>lt;sup>2</sup> The use of will is deprecated and cannot be used when stating mandatory requirements; will is only used in statements of fact.

#### 2. Normative references

The following referenced documents are indispensable for the application of this document (i.e., they must be understood and used, so each referenced document is cited in text and its relationship to this document is explained). For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments or corrigenda) applies.

Accellera VAMS-2023, Verilog-AMS Language Reference Manual.<sup>3</sup>

IEEE Std 1800™, IEEE Standard for SystemVerilog—Unified Hardware Design, Specification, and Verification Language. 4,5

IEEE Std 1800.2<sup>TM</sup>, IEEE Standard for Universal Verification Methodology Language Reference Manual.

# 3. Definitions, acronyms and abbreviations

#### 3.1 Definitions

For the purposes of this document, the following terms and definitions apply. The normative references in Clause 2 and the *IEEE Standards Dictionary Online* should be consulted for terms not defined in this clause. <sup>6</sup>

**AMS:** Analog/Mixed-Signal (AMS) simulation and verification refers to systems that can simulate and verify analog/mixed-signal designs using co-simulation of digital (*logic* or *real* data types) event-driven engines and analog (*electrical* data types) time-domain solvers ("AMS co-simulation").

**Blocking, non-blocking:** A *blocking* task call suspends execution until it completes. A *non-blocking* call returns immediately.

**Bridge core:** A module in the MS Bridge that performs data type conversion and manipulation between the UVM agent and the DUT. This can include modeling of passive and active analog components. It is the bridge core that directly connects to and drives the DUT.

**DMS/RNM:** Digital (or Discrete)/Mixed-Signal (DMS) simulation and verification refers to event-driven systems that can simulate and verify analog designs using discrete abstractions of the analog design. Such designs can use SystemVerilog *user-defined net types* (*UDNs*) and/or *real* variables to represent the analog intent. There is no standard on how discrete modeling of analog nets should be done, so the examples given here are just one method of implementation. Sometimes the term RNM (Real-Number Modeling) is used. The term DMS will be used to refer to both DMS and RNM within this document.

**MS:** Mixed-Signal (MS) simulation and verification refers to verification of a DUT that is made up of digital and analog blocks. These analog blocks could be transistor designs or a model abstraction utilizing DMS, AMS or a mixture. The focus of this standard is to support MS rather than specifically DMS or AMS.

**OOMR:** An Out-of-Module Reference (OOMR) is a reference from one module to another. Sometimes called XMR (Cross-Module Reference).

**Proxy:** A class functioning as an interface to another **component** or class.

**UVM:** The Universal Verification Methodology that enables creation of robust, reusable, modular and interoperable verification IP and testbench components for digital verification. UVM is documented in IEEE Std 1800.2.

<sup>&</sup>lt;sup>3</sup> Accellera publications are available from the Accellera Systems Initiative (https://accellera.org/).

<sup>&</sup>lt;sup>4</sup> IEEE publications are available from the Institute of Electrical and Electronics Engineers (<a href="https://standards.ieee.org/">https://standards.ieee.org/</a>).

<sup>&</sup>lt;sup>5</sup> The IEEE standards or products referred to in Clause 2 are trademarks owned by the Institute of Electrical and Electronics Engineers, Incorporated.

<sup>&</sup>lt;sup>6</sup> IEEE Standards Dictionary Online is available at: <a href="http://dictionary.ieee.org">http://dictionary.ieee.org</a>. An IEEE Account is required for access to the dictionary, and one can be created at no charge on the dictionary sign-in page.

**UVM-MS:** A comprehensive and unified mixed-signal verification methodology based on UVM to improve AMS and DMS verification of integrated circuits and systems.

## 3.2 Other acronyms and abbreviations

API Application Programming Interface

DC Direct Current

DUT Device Under Test

IF Interface

I/O Input/Output

IP Intellectual Property

PWL Piecewise-Linear

SV SystemVerilog

UDN User-Defined Nettype

#### 4. UVM-MS architecture

#### 4.1 Introduction

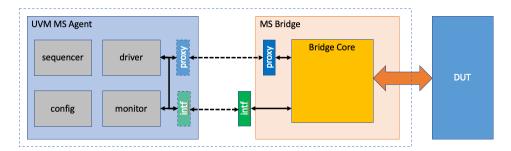

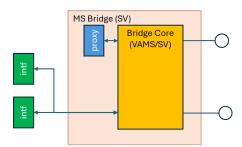

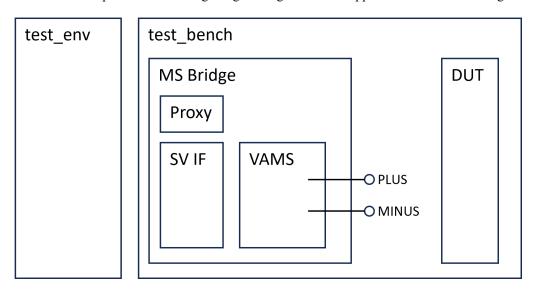

The structure of a generalized UVM-MS agent and its connection to a mixed-signal DUT are shown in Figure 1 below. A UVM-MS agent differs from a digital-only UVM agent in that it contains a handle to a proxy class in addition to the virtual interface to communicate with the DUT. The MS Bridge is the layer between the agent and the mixed-signal DUT.

The MS Bridge is a System Verilog module comprising a proxy class object (the MS Proxy), a System Verilog interface (the SV IF), and a Bridge Core module. The bridge core performs signal data type conversion and manipulation between the UVM agent and the DUT. This can include modeling of passive and active analog components. It is the bridge core that directly connects to and drives the DUT. The proxy class provides an API that conveys analog attributes between the agent and the bridge core. The SV IF is used only for passing logic-type (i.e., not real or user-defined nettype values) between the agent and the bridge core, whereas the proxy is used to drive values for controlling analog signal generation or to monitor aspects of the analog signal.

Figure 1: UVM-MS Architecture

The agent contains a handle to the MS Proxy and a virtual interface to the SV IF. The dashed lines in the diagram indicate communication via these mechanisms. The MS Proxy and SV IF can be used together or individually, depending on the types of connections required. The SV IF may be placed either within the MS Bridge or between the agent and the bridge. This document presents only one of those options in most places, but unless stated otherwise, both are possible. See Clause 5 for more details.

The bridge core can be modeled with SystemVerilog, Verilog, or Verilog-AMS, based on the net types of the DUT I/O it connects to. The choice of the modeling abstraction for the bridge core is made at elaboration time. The bridge may contain more than one bridge core, of the same or different types. Each core may connect to one or more SV interfaces. However, a bridge contains only one proxy, regardless of the number of cores inside.

As mentioned above, some changes are necessary to UVM drivers, monitors, and other objects to accommodate the handle to the proxy class and use it appropriately. If a testbench already exists, this can be done by deriving a mixed-signal enhanced version of the digital component and using UVM factory overrides to replace the originals. Then a modest set of changes can add the critical capabilities without disrupting any other purely digital applications of the UVM collateral.

## 4.2 MS bridge

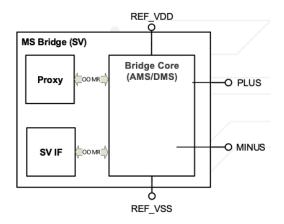

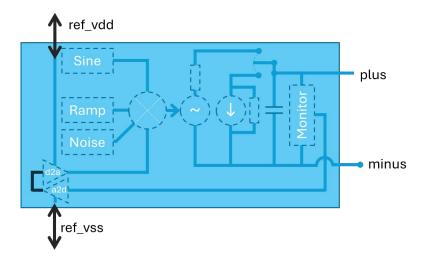

UVM-MS introduces the concept of an MS Bridge, whose sole purpose is to create a bridge between the UVM-MS agent and the DUT, since direct connection via an SV interface is not possible for all DUT I/O abstractions. An example of a bridge is shown below in Figure 2. It uses the analog attributes from the proxy to generate continuously changing values (e.g., ramping voltage supply, electrically modeling drive strengths, R/C loading, etc.) in the bridge core

Figure 2: Example MS Bridge

The MS Bridge is written in SystemVerilog and shall contain the bridge core instance. The bridge core may use SystemVerilog or Verilog-AMS data types to drive the DUT pins. The bridge core abstraction can be changed and the existing UVM-MS framework will not require any other changes as long as the API is kept the same.

Although different abstractions of the bridge core can be used, Verilog-AMS only supports a limited set of port data types, so the SV interface and the proxy shall connect to the bridge core using OOMRs, to avoid these restrictions. These OOMRs shall only refer to constructs found in Verilog-AMS, which are common to all abstractions (but less limited than Verilog-AMS port data types).

The DUT I/O of the MS Bridge shall be defined as SystemVerilog **interconnect** types. The net type of the bridge DUT I/O should be resolved from the types of its connections, which may vary with the model abstraction level, so defining ports as **interconnect**, which is typeless, allows the simulator to do this and also prevents OOMRs and probes to them. Unless it is certain that the direction will always be unidirectional (**input** or **output**), it is recommended that the direction be declared as **inout**, which is more precise and is portable with electrical modeling.

While the MS Bridge is written in SystemVerilog, the DUT ports and the Bridge Core ports may be Verilog-AMS data types that are not supported in SystemVerilog. In order to support UVM-MS, the simulation tool needs to support connections of the Bridge Core to the DUT of such data types through the MS Bridge I/O.

The MS bridge ports and the bridge core ports to the DUT shall not be unpacked arrays, which are not supported by Verilog-AMS. For the same reason, ports may have only one packed array dimension.

#### **4.2.1 MS proxy**

In UVM, SystemVerilog *interfaces* are used to allow communication between the class-based portion of the testbench and the DUT. There are several shortcomings with interfaces that impact mixed-signal verification:

- Setting parameters on an interface (e.g., for analog component values) results in a specific data type that ripples through UVM configuration, hampering reuse.

- Implementing a bridge core API in an interface limits reuse, as it is impossible to override methods.

- It is not possible to communicate with Verilog-AMS code via an interface.

Due to these shortcomings, an alternative approach, the MS Proxy, is used. The MS Proxy in the MS Bridge follows the abstract/concrete class design pattern. The **uvm\_ms\_proxy** definition is provided within the **uvm\_ms\_pkg.sv** file (see A.1). An abstract extension of **uvm\_ms\_proxy** is then declared with prototypes of a set of methods that form the API through which a UVM-MS agent communicates with the MS Bridge.

Example:

```

import uvm_ms_pkg::*;

virtual class vdriver_proxy extends uvm_ms_proxy;

pure virtual function void set_voltage(...);

pure virtual function real get_voltage(...);

pure virtual function void push(...);

pure virtual function void pull(...);

. . .

endclass: vdriver_proxy

```

The concrete version of the proxy class is declared in the MS Bridge and extends the abstract version, implementing the API methods. A handle to the concrete proxy class is assigned to an abstract class handle in a UVM agent using the **uvm\_config\_db**. Polymorphism allows the UVM agent to handle different implementations of the abstract class without modification, e.g., implementations to suit DMS/AMS models of bridge cores.

Example:

```

module vdriver_bridge(PLUS, MINUS);

...

vdriver_core #(...) i_core (...); // MS model

class MSproxy extends vdriver_proxy;

virtual function void set_voltage(...);

...

endfunction: set_voltage

...

endclass: MSproxy

MSProxy i_proxy = new("i_proxy");

...

endmodule: vdriver_bridge

module hw_top;

...

vdriver_bridge i_vdriver_bridge (.PLUS(vcc),.MINUS(gnd));

...

endmodule: hw top

```

```

class tb extends uvm_env;

...

function void build_phase(uvm_phase phase);

uvm_config_db#(vdriver_proxy)::set(null, "uvm_test_top.env", "vdriver_proxy",

i_driver_bridge.i_proxy);

...

endfunction

...

endclass: tb

```

A typical MS Proxy API contains methods to implement the following features, described in more detail in Clause 6:

- **Pull** (read) bridge core values via function calls to the bridge core.

- **Push** (write) bridge core attributes using function calls to the bridge core.

- Push-Sync contains registers for end-of-transition detection or other synchronization from bridge core control.

- Monitor continuous signals.

#### 4.2.2 SV interface

The existing SV interface can continue to be used for logic-type communication normally used for UVM, thus enabling reuse of existing verification collateral. There is a limitation on bidirectional signals, which requires the driver and receiver part of the net to be manually split.

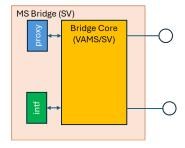

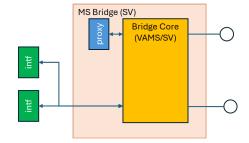

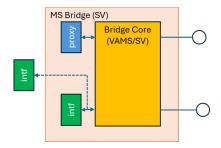

The SV interface can be located inside the MS bridge or outside the bridge, between the UVM agent and the bridge. See Figure 3 and Figure 4. Each method has certain advantages.

Figure 3: SV interface inside bridge

Figure 4: SV interface outside bridge

Example code of an SV interface outside the bridge:

```

interface my_intf;

...

endinterface

module tb;

my_intf i1();

ms_bridge i2(.my_if(i1),.PLUS.....);

// + DUT instantiation

endmodule

module ms_bridge(inout interconnect PLUS, ..., interface my_if);

// SV IF to Core connections that are bidirectional

my_short i1(my_if.a, core.net1);

my_short i2(my_if.b, core.net2);

// + Proxy declaration and instantiation

// + Core instance

endmodule

```

The SV interface is discussed in more detail in Clause 5.

## 4.2.3 Bridge core

The MS testbench may require the behavior and presence of passive and active analog components that a typical UVM-RTL testbench could not include, such as:

- Capacitors, resistors, inductors, diodes, current/voltage sources, etc.

- A complex passive network

- A piece of Verilog-AMS code

Such components will be used to model the analog behavior of pads, lossy transmission lines, loads/impedances, voltage/current-controlled sources, etc., required to accurately model the signals connecting to the ports of the DUT. Those components can be placed inside the bridge core, to be controlled by the proxy.

In Figure 2, the example bridge core has four pins. PLUS and MINUS are two typical terminals on a component, which could be a voltage/current source or a capacitor, for example. REF\_VDD and REF\_VSS allow a logic input from the SV IF to be converted to a voltage relative to these values. In the MS Bridge, these ports are declared as **inout interconnect**, so the actual net types are determined by their connections, in this case, the bridge core ports and the DUT ports.

In AMS, the bridge core could instantiate SPICE primitives or Verilog-A modules<sup>7</sup>; however, this restricts presimulation changes in component values that are possible during the UVM pre-run phases if bridge core functionality is instead written using Verilog-AMS analog contribution statements.

In DMS, there are no restrictions. Verilog-A modules can be compiled as Verilog-AMS, and the predefined Verilog-AMS macro `\_\_vams\_enable\_\_ allows Verilog-AMS-only code to be excluded when the same file is parsed as Verilog-A. An example where a SPICE primitive might be needed is when a printed circuit board component is

<sup>&</sup>lt;sup>7</sup> Accellera VAMS-2023, Verilog-AMS Language Reference Manual, Annex E.

supplied as a SPICE model. It is recommended to use Verilog-AMS analog statements to implement the electrical functionality whenever possible.

The SV interface and the proxy shall connect to the bridge core with OOMRs, because Verilog-AMS only supports a limited set of port data types and does not allow unpacked array ports. The SV interface may use direct OOMRs to variables or wires in the bridge core, but the proxy should call functions defined in the bridge core. An example of when a function cannot be used is when a bus of reals needs to be passed into the bridge core, as Verilog-AMS does not support this. Another exception is shown in 6.1.5, where a bridge core synchronization variable is directly assigned to a proxy variable.

#### 4.2.3.1 Driving continuous analog signals

Perhaps the major difference between digital and analog simulations is that digital signals tend to change discretely, whereas analog signals may be continuously changing. Many useful analog signals can be composed of other periodic waveforms, such as a series of sine waves. Taken to the extreme, a square wave, which is modeled digitally as "set to 1; wait a short time; set to 0; wait a short time," etc., could actually be modeled as an infinite series of harmonic sine waves, although it would never actually be implemented that way.

In practice, a sine wave can be controlled simply by four values defining the frequency, phase, amplitude, and DC bias of the generated signal. A UVM transaction can be defined that encodes the properties of the desired sine wave as real values in the **uvm\_sequence\_item**. This item can then be passed to the UVM driver, which will in turn pass the values to the MS Bridge Core via the MS Proxy. The Bridge Core will use those values to generate the signal.

In general, to drive such a continuous signal, the **uvm\_sequence\_item** would contain fields for all desired control parameters of the desired analog signal, and the driver will drive those settings through the proxy class to the MS Bridge Core to control the signal generator, which should be located in the domain of the DUT I/O it will connect to. For example, an analog sine wave should be implemented in the analog domain although controlled from the digital domain.

In this way, the UVM paradigm of having a relatively simple interface for the test writer is continued, providing a way to control the generated signal as needed.

#### 4.2.3.2 Multiple signal generators

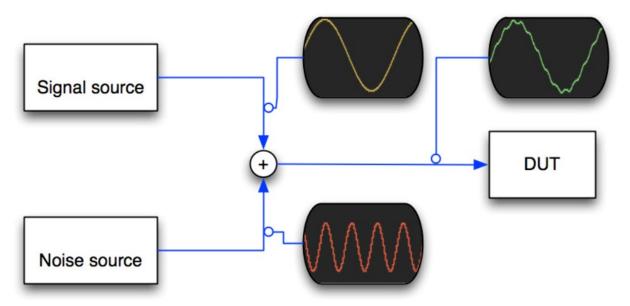

It is possible to combine multiple signal generators to create more complex signals. For example, a signal source may be defined to be a sine wave, as described in the previous section. An additional requirement may be to inject some noise onto that signal. There are several ways to implement this. The noise source may use a different **uvm\_sequence\_item** and may be controlled as part of the main UVM sequence, which could be used to inject noise at predictable intervals within the sequence. Alternatively, it may be generated by a different sequence, where the noise might be injected randomly. In either case, the driver will detect the sequence items as either signal or noise and pass the appropriate information on to the signal generator(s), depending on the environment.

Figure 5: Multiple analog drivers on a single net

#### 4.3 UVM-MS agent

In general, adapting a pure digital UVM agent for UVM-MS potentially requires extensions and factory overrides of the agent, driver, monitor, and sequence item classes.

The UVM-MS agent is in effect no different from a **uvm\_agent**. However, some design choices can simplify extension to allow operation with an MS DUT. For example, the handles to the MS proxy class and the virtual interface can be contained in the agent configuration object. If there is an existing agent, it can be extended to create the MS agent.

Example:

```

class osc_ms_agent extends osc_agent;

```

#### 4.3.1 UVM-MS driver

The UVM-MS driver is responsible for requesting and driving transactions from/to the agent sequencer. Driving can involve communication with an MS proxy and/or an SV interface. Patterns for implementing the communication are described in Clause 6. If there is an existing driver, it can be extended to create the MS driver.

Example of a driver call to a *push* method defined in the proxy:

```

virtual task drive_transaction(osc_ms_transaction req);

...

bridge_proxy.push(.ampl(req.ampl),.bias(req.bias),.freq(req.freq));

...

```

#### 4.3.2 UVM-MS monitor

A UVM-MS monitor extends the UVM monitor by adding a handle to the MS Proxy. The MS Proxy supports DMS/AMS DUT connections by implementing *pull* and *monitor* methods, as described in Clause 6. Logic signals transferred via the SV IF can be monitored using the existing methods in UVM. If there is an existing monitor, it can be extended to create the MS monitor.

Example:

```

class osc_ms_monitor extends osc_monitor;

```

#### 4.3.3 UVM-MS sequence item

The sequence item used by the UVM-MS agent will likely have additional fields that will be used by the MS proxy.

Example:

```

class osc_ms_transaction extends osc_transaction;

rand real ampl;

rand real bias;

...

```

#### 4.4 UVM-MS scoreboard and coverage

Scoreboard and coverage architecture may not need to change. However, they may need to be extended to add additional checks or to take into account additional information found in the extended transaction type.

Example:

```

class osc_ms_scoreboard extends osc_scoreboard;

```

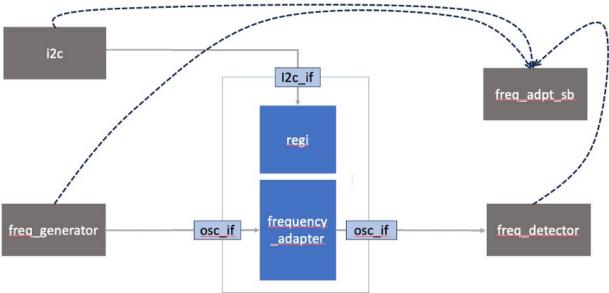

#### 4.5 UVM-MS testbench

The testbench needs to be extended to add the **uvm\_config\_db** call to pass the proxy handle and the **set\_override** calls to specify the overrides for any scoreboard, agent, driver, monitor, and sequence item that have been extended.

The following example is excerpted from the frequency adapter example in Annex B:

```

class freq adpt ms tb extends freq adpt tb;

`uvm component utils(freq adpt ms tb)

function new (string name, uvm component parent=null);

super.new(name, parent);

endfunction : new

// UVM build() phase

virtual function void build phase(uvm phase phase);

// set up bridge proxy pointer references in generator & detector agents

uvm config db #(osc proxy)::set(this,"freq generator.agent.*",

"bridge proxy", top.generator bridge.proxy);

uvm config db #(osc proxy)::set(this,"freq detector.agent.*",

"bridge proxy", top.detector bridge.proxy);

\ensuremath{//} override driver, monitor, and scoreboard with UVM-MS versions

set_type_override_by_type(osc_transaction ::get_type(),

osc_ms_transaction ::get_type());

set_type_override_by_type(osc_driver

::get_type(),

freq adpt ms scoreboard::get type());

```

```

super.build_phase(phase);

endfunction : build_phase

endclass: freq_adpt_ms_tb

```

## 5. Bridge configuration

The MS Bridge DUT I/O ports shall be of type **interconnect**, which disallows probes or assignments to these ports at this level. All probes and assignments should be done in the bridge core that is instantiated in the MS Bridge. Declaring the port as the typeless **interconnect** not only prevents OOMRs, but also means that the net type will be resolved from its connections. It is recommended that the direction be **inout**.

Classical UVM has SystemVerilog interfaces instanced along with the DUT in a module. The DUT ports can be connected to an instanced interface as individual port connections or themselves be grouped as a port of **interface** type. If the DUT ports are an interface, then for UVM-MS, these shall only contain logic-type data types and do not require a MS Bridge, as these ports cannot have any other abstraction.

UVM-MS supports the SV IF instanced inside the MS Bridge or external to the bridge. The SV IF shall only contain integral signals.

If the SV IF is external to the MS Bridge (Figure 6), this allows multiple types of interfaces to be hooked up, e.g., in a scenario where the DUT I/O could be used for multiple digital communication functions. For example, a group of pins might work with I2C or with SPI. This allows the MS Bridge to be a generic connector decoupled from the digital side.

In this configuration, the SV IFs connect to MS Bridge ports. Within the bridge, these ports connect to the bridge core with OOMRs, not with ports, just as the MS Proxy connects to the core with OOMRs. This configuration enables the insertion of the MS Bridge between the DUT and SV IF as a simple step from UVM to UVM-MS. However, the hierarchical path to the SV interfaces is then different from the path to the proxy and the bridge.

Figure 6: SV interface connection external to bridge

If the SV IF is internal to the MS Bridge (Figure 7), an external IP provider only has to supply a single module to instantiate with the DUT. This has the advantage that encryption is easier and the hierarchical paths to the proxy and the interface are the same.

Figure 7: SV interface connection internal to bridge

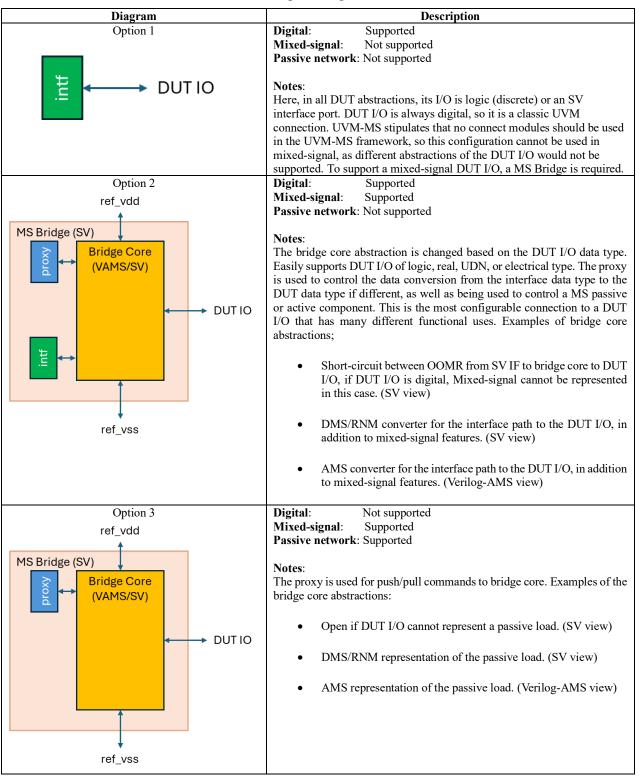

Table 1 below shows the various possible configurations of the MS Bridge. In each case, the SV IF is shown within the MS Bridge, but as discussed above, it could be external to the bridge.

The table describes the configuration assuming a single DUT port abstraction type. However, an MS Bridge could have multiple types of DUT I/O connections that make up a protocol, e.g., a mixture of multiple supplies and logic signals, such as USB. A bridge could also have more than one core internally.

In the table, DUT I/O type abstractions are divided into two kinds: *digital*, whose DUT I/O abstraction is made up of 2-state or 4-state *logic* types, whether individually or as part of an SV interface port, and *mixed-signal*, whose abstraction can use *reals* or *wreals* (RNM), *UDNs* (DMS) or *electrical* (AMS). A subtype of mixed-signal is when the port is a pure analog *passive network*.

A *Passive network* refers to the use case where the bridge controls an analog passive network in the bridge core needed for the DUT, such as a speaker model. The analog passive network can be made up of many controllable components, such as L/R/Cs. An example is a resistor used as a switch or variable resistance between two DUT pins.

*Mixed-signal* types can contain, for example, multiple sources of stimulus, such as controlling the data type conversion of the interface to the DUT I/O (slew rate, A2D/D2A logic levels, output drive impedance, etc.) and driving a voltage or current with some waveform representation (see Figure 8).

Figure 8: Mixed-signal bridge

Table 1: Bridge configurations

Passive analog components, such as capacitors, resistors and inductors, often have their value set once and left unchanged during the simulation. A typical setup would use parameters on the instance to set their default values. This

makes the values easier to review. To avoid coding the default values for these components in the agent, functions are used to read the parameter values and to store them in the **uvm\_config\_db**. In the following example, the **get\_parameters()** function in the proxy is used to read all the parameters and pass them back to the agent to apply them to the **uvm\_config\_db** in the UVM *connect* phase. If a testcase requires a change, the values are changed by a call to **set\_parameters()** in the UVM *start of simulation* phase, before time is consumed.

The bridge core has internal variables that are initialized to the parameter values, but can be later overridden by a **set\_parameters()** function call (recommended) or by an OOMR. These variables are the values that are used in the subsequent code. The **get\_parameters()** function reads the initial values of the bridge core variables to ensure that any **defparam** statement override is considered. It is recommended that the configuration be written out, as a mistake in the values could be hard to debug.

Example:

```

package res pkg; // This package contains definitions of common variables and types

class res config extends uvm object;

real res val, res tr, res tf;

`uvm object utils(res config)

function new(string name = "res config");

super.new(name);

endfunction : new

endclass: res config

virtual class res proxy extends uvm ms proxy;

pure virtual function void set parameters(res config cfg);

pure virtual function res config get parameters();

endclass: res proxy

endpackage: res pkg

module ms_bridge #(parameter real res_val=1.0, res_tf=1.0e-9, res_tf=1.0e-9)

(inout interconnect PLUS, MINUS);

import uvm pkg::*, uvm ms pkg::*;

`include "uvm macros.svh"

`include "uvm_ms_includes.svh"

import res pkg::*;

//-----

// API implementation of the proxy that the MS agent connects to

//-----

class MSproxy extends res proxy;

function new(string name);

super.new(name);

endfunction: new

// Function to get initial values for config db taken

// from bridge core in case a defparam has been used

virtual function res config get parameters();

res config cfg = new();

cfg.res val = i core.rseries val;

```

```

cfg.res_tr = i_core.rseries_tr;

cfg.res tf = i core.rseries tf;

return(cfq);

endfunction: get parameters

// Function to set initial values from config class

// into bridge core after modification by uvm test

virtual function void set_parameters(res_config cfg);

i_core.rseries_val = cfg.res_val;

i_core.rseries_tr = cfg.res_tr;

i_core.rseries_tf = cfg.res_tf;

endfunction: set parameters

// Other code

endclass: MSproxy

// Instantiate proxy class

MSproxy i proxy = new("i proxy");

// instance of bridge core

bridge_core i_core #(.res_val(res_val),

.res_tr (res_tr) ,

.res tf (res_tf))

(.PLUS (PLUS), .MINUS (MINUS));

endmodule: ms bridge

Bridge Core:

`include "constants.vams"

`include "disciplines.vams"

module bridge core (PLUS, MINUS);

// Values read by get parameters() in MS Bridge

parameter real res va\overline{l} = 1.0;

parameter real res tr = 1.0e-9;

parameter real res tf = 1.0e-9;

// Initial values set from parameters, then overriden by set parameters()

// Code uses rseries * variables

real rseries_val = res_val;

real rseries_tr = res_tr;

real rseries_tf = res_tf;

endmodule

```

## 6. Bridge core communication

The goal of the bridge core communication is that it should work whatever the abstraction of the bridge core is. The Proxy/SV interface connection to the bridge core needs to be the same for any bridge core abstraction, so that the abstraction can be changed without affecting the rest of the agent and the MS Bridge. Thus, any abstraction needs to implement the same functions. This also leads to the code having to conform to the subset that is common to both SystemVerilog and Verilog-AMS.

Therefore, the **uvm** hdl \* methods shall not be used to read or write the logic variables.

Section 6.1 discusses communication in an AMS environment and section 6.2 describes communication in DMS.

#### **6.1 AMS communication**

Verilog-AMS defines ways in which continuous analog domain signals can update values that are then used in the digital domain. The Verilog-AMS system functions to do this are cross(), above(), and absdelta(), which can be used in a digital @() statement (above() is strongly preferred over cross()). This portion is the A->D trigger direction, in that the analog domain will generate the event for the digital domain to use. Use cases are:

- Event generation from analog signals (cross(), above(), absdelta())

- Quantized continuously monitored analog signals (absdelta())

Verilog-AMS defines how the discrete domain can read analog values and how digital inputs shall be interpreted by the analog domain. Digital inputs that are read by the analog domain should be filtered by a **transition()** function to smooth out the discrete change into a PWL signal. This portion is the D->A trigger direction, in that the discrete domain will generate the event for the analog to then use. These can be categorized into the following use cases;

- Pull (read) analog values via event-driven calls (do not cause an analog timestep, and values are interpolated)

- **Push** (write) bridge core controls

- Push bridge core controls with handshake synchronization

Combinations of A->D and D->A triggers can be used, e.g., an A->D event being used to pull an analog value causes a D->A event. The subtleties are discussed in the next section to ensure robust communication. The UVM-MS methodology does not dictate how this is done, but points to possible "gotchas" that are often missed.

#### 6.1.1 Event generation from analog signals

Events in the digital domain can be generated from analog signals in two ways. In the first way, a **cross()** or **above()** function call can be used to generate a digital event when an analog signal meets the requirements for the function to trigger the event. This method is useful, for example, when the exact point the signal goes out of range is required, but at a performance cost.

Example:

```

always @ (above(V(in)-0.9,...) or above(0.5-V(in),...)) -> out_of_range;

```

The second way is when the nearest analog timestep is good enough, in which case the following code is suitable. The absdelta() function is used to sample the analog value out\_of\_range\_ana when its value toggles between 0 and 1. The advantage of this approach is that it does not affect the analog time step algorithm.

NOTE—In Verilog-AMS, an event occurs whenever a value is assigned to an analog variable that appears in a @ () event control, regardless of whether the variable changes value or not, so triggering off out\_of\_range\_ana directly would cause an event at every analog timestep regardless of whether the value changed or not.

## 6.1.2 Quantized continuously monitored analog signals

Verilog-AMS provides the function absdelta() to quantize an analog signal for use in the discrete domain. The absdelta() function provides controls how to do the quantization as well as an enable. In addition, it is possible to query the analog value from the discrete domain by an event, such as a periodic clock. The choice between absdelta() and a periodic sampling depends on the use case and on the signal to achieve optimal simulation performance. Some examples are shown below; there is no generic solution that can be applied. See the Verilog-AMS standard for a comprehensive description of the absdelta() function.

Setting the *delta*, *time\_tol* and *expr\_tol* arguments appropriately allows **absdelta()** to operate accurately. Using a periodic digital event to sample the value may seem simpler, but each query causes a request to the analog solver to interpolate the *analog\_expr* to get a value for that digital time point. Each request for the analog value is a blocking request, so control passes to the analog solver to get the value before returning to the digital solver.

#### 6.1.3 Event-driven queries of analog values

It is possible to use a digital function within a Verilog-AMS file to probe continuous variables or nets. The returned value is interpolated from the last accepted matrix solution and the next proposed solution. The proxy would use a function call to the function in the bridge core to return the value. (Note that functions in Verilog-AMS are required to have at least one input, even if not needed, and support only a limited set of data types.)

```

function real get_voltage(input dummy);

begin

get_voltage = V(PLUS);

end

endfunction

function real get_current(input dummy);

begin

get_current = I(<PLUS>);

end

endfunction

```

#### 6.1.4 Push analog control

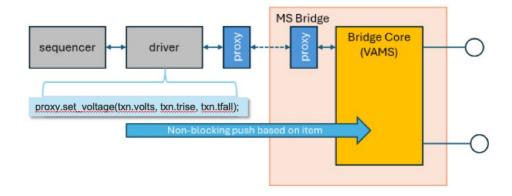

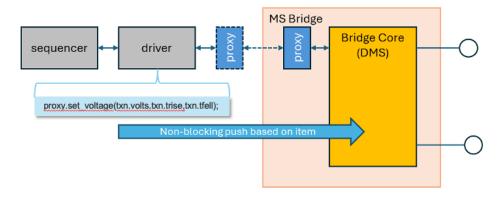

#### Figure 9: Push pattern for analog control example

The **push** pattern for analog control makes an instantaneous change to discrete bridge core variables and does not wait for an event or a signal change to happen before returning. The agent driver simply calls a function in the proxy class that in turn either calls a function in the bridge core or uses an OOMR to set the value of a variable internal to the bridge core. The proxy function then immediately returns control to the driver. In Figure 9, txn is a transaction instance name.

#### 6.1.5 Push analog control with handshake (push-sync)

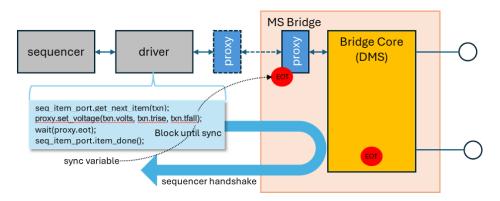

Figure 10: Push-sync pattern for analog control example

The **push-sync** mechanism synchronizes the digital and analog simulation engines, since the analog solver requires time to change signal values. This pattern drives a change to the bridge core and waits for an event based on a signal condition before passing control to the next sequence item. This can be useful for such operations as voltage ramping, etc.

**NOTE** (informative): The example shown in Figure 10 uses wait(proxy.eot) rather than a delay that matches the transition time to allow for potential tolerances in the analog solver that may cause the final value to be reached slightly before of after that actual transition time specified. In addition, the set\_voltage() call used in the example could be a combination of other changes in the Bridge Core that monitors for completion.

A push-sync pattern implementation shall declare a synchronization variable in the bridge core that indicates when the event has occurred, and a corresponding synchronization variable in the proxy class. The driver waits for the proxy synchronization variable before continuing.

Use function calls to prevent race conditions. A function does not return until its nested function calls have also completed.

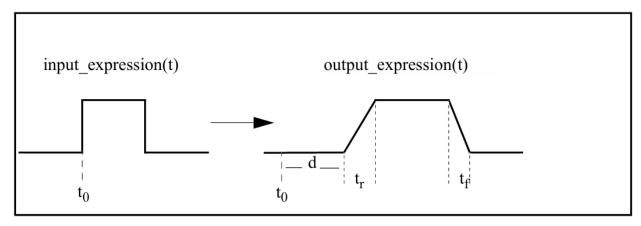

For example, the transition filter **transition()** in Verilog-AMS smooths a discrete signal into a continuous-time signal. It stretches instantaneous changes in signals over a finite amount of time and can delay the transitions, as shown in the following figure.

Figure 11: Verilog-AMS transition filter

Within Verilog-AMS, there is no signal to say that the transition filter has completed, even though the simulator has that information. But Verilog-AMS code can detect whether the transition filter has completed, which is useful feedback to an agent. The input value to the transition filter can be compared to the output, and when they are within a certain tolerance, the filter can be deemed to have completed.

In the example below, the driver passes a voltage change to the Verilog-AMS bridge core via the proxy. The set\_ramp\_voltage function in the proxy calls the corresponding function in the bridge core. It waits for the bridge core function to complete, initializes the "end of transition" flag vdc\_eot, and then returns to the driver. The driver waits for the flag to become 1.

```

// in the driver

proxy.set ramp voltage(5.0);

wait(proxy.vdc eot);

module ms bridge .....

ms bridge core icore (...); // instantiation of the bridge core

class MSproxy extends vdriver_proxy; // vdriver_proxy defines int vdc_eot

function automatic void set ramp voltage (real val, tr = 1e-9, tf = 1e-9);

void'(i core.set ramp voltage(val, tr, tf));

vdc_eot = i_core.vdc eot;

endfunction: set ramp voltage

MSproxy i proxy = new("i proxy");

endclass

// Capture changes from the bridge core and copy to proxy.

// @(...) at the end so that i proxy.vdc eot is assigned when the process starts.

// This saves an assignment initialization statement.

always begin

i proxy.vdc eot = i core.vdc eot;

@(i core.vdc eot);

end

endmodule

// Verilog-AMS

module ms bridge core ....

function automatic integer set ramp voltage(input real val, tr, tf);

begin

vdc

= val;

vdc_tr = tr;

vdctf = tf;

```

```

vdc_eot = (abs(vdc_tran - vdc) < tol) ? 1:0; // Update vdc_eot

set_ramp_voltage = 1; // Return 1; V-AMS does not have void functions

end

endfunction

integer analog_clk;

analog begin

vdc_tran = transition(vdc, 0, vdc_tr, vdc_tf);

// A change in vdc is a D2A even, triggering the analog solver.

...

analog_clk = 1 - analog_clk; // Generate signal to update vdc_eot

end

// Update vdc_eot on every analog timestep.

always@(absdelta(analog_clk,1,0,0)) vdc_eot = (abs(vdc_tran - vdc) < tol) ? 1:0;

...

endmodule</pre>

```

In this example, vdc is a real value passed from the agent into the bridge core as a digital owned variable. vdc\_tran is the output of the transition filter and is a continuous real variable. At each analog timestep, the output of the transition filter is updated and vdc\_eot is recalculated. vdc\_eot determines whether the continuous variable is within a tolerance of the discrete value. A tolerance is needed as the comparison is on two real numbers. In this case, the two real numbers represent voltages, so the recommendation for tol is the Verilog-AMS abstol for that discipline.

## 6.1.6 Pull analog value

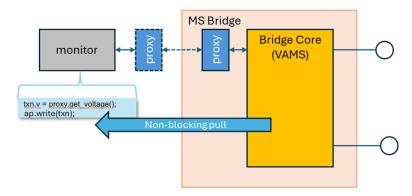

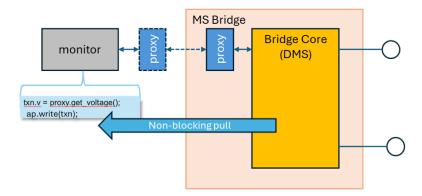

Figure 12: Pulling a value from the bridge core

The pull pattern takes an instantaneous measurement from the bridge core such that it is suitable for a UVM monitor. It is recommended that the monitor call a function in the proxy that in turn calls a function in the bridge core. In Figure 12, ap is the instance name of a *uvm analysis port*.

#### 6.2 DMS communication

DMS as defined in this document uses native SystemVerilog constructs, and could have been set up without a bridge and then the testbench and data communication would be simpler. However, in many cases, a DMS model either needs to use an AMS model as a baseline to fine-tune its behavior, or both models need to run interchangeably. These cases require setting up the DMS bridge core communication to be functionally identical to the AMS version and to inherit the Bridge Core-Proxy-Agent communication pattern described above. Based on this principle, the HDL and UVM testbench hierarchies could remain the same while switching between AMS and DMS modules at elaboration time.

This section describes how to implement in DMS the same communication patterns described in the previous section for AMS.

#### 6.2.1 Event generation from analog signals

In DMS, digital events could be generated by monitoring value changes of variables. However, the user needs to guard against an excessive number of events due to noise. It is therefore important to utilize some tolerance. There are multiple ways to achieve this, e.g., instead of simply @(myvar), it could be better to write "@(abs(myvar - myvar prev) - tol)" on a sensitive signal, where abs() is a user-defined absolute value function.

Dedicated modules can also be created to achieve these kinds of monitoring. For simplicity, a delay could also be used for stimuli with predetermined duration (e.g., PWL or periodic waveforms) where end-of-signal transitions do not necessarily indicate the end of the transaction. One useful programming pattern is to set the timescale of the module to, e.g., one second, with a timeunit statement. A delay could then be sent from the UVM side in units of seconds, and the delay implemented as # (delay exp in sec \* 1s).

## 6.2.2 Quantized continuously monitored analog signals

In DMS, analog signals can be directly monitored.

## 6.2.3 Event-driven queries of analog values

In order to preserve the function signatures and ensure a smooth transition between DMS and AMS, the proxy is used to query values from the bridge core. DMS implementations need to accommodate the same set of functions. The exact implementation of such functions may depend on the abstraction.

For example, when the analog output is modelled with the VIZ\_wire user-defined nettype, the API could be defined as:

```

typedef struct {

real V;

real I;

real Z;

} VIZ type;

nettype VIZ type VIZ wire;

module ms bridge core(inout VIZ wire p);

function real get voltage(input dummy);

begin

get voltage = p.V;

end

endfunction: get voltage

function real get current(input dummy);

begin

get current = p.I;

end

endfunction: get current

endmodule

```

## 6.2.4 Push analog control

Figure 13: Push analog control - DMS version

As in AMS, the driver calls a method in the proxy class to make an instantaneous change to a bridge core value and then returns control to get the next sequence item. The **set\_voltage()**/**get\_voltage()** functions could remain mostly the same.

Similar to the transition filter in Verilog-AMS, in DMS one could create a dedicated function to control the updates to the voltage magnitude and frequency actually driven to the DUT and ensure that the changes are smooth. Instead of directly writing changes to the core module, the changes are intercepted and filtered by intermediate signals. This could improve performance by preventing too-frequent writes that would force the analog solver to reevaluate the analog matrix.

## 6.2.5 Push analog control with handshake (push-sync)

Figure 14: Push-sync pattern for analog control example - DMS version

This push-sync pattern is similar to that of the AMS version. In the bridge core, the value update could be interpolated in a fashion similar to that of a transition filter.

## 6.2.6 Pull analog value

Figure 15: Pulling a value from the bridge core - DMS version

This pattern is also similar to that of AMS. In AMS, these queries need to be carried out by access functions, whereas in DMS, bridge core variables can be queried directly. User can also incorporate current or resistance with user defined net types into the model and enable queries of such signals.

#### 7. Messaging

#### 7.1 General

Users need the ability to report what is happening during simulation. Users may want to display:

- Errors, both in creating the verification environment and in simulation results

- Debug messages, to help understand why problems have occurred

- Progress reports, to show that the simulation is doing what it should

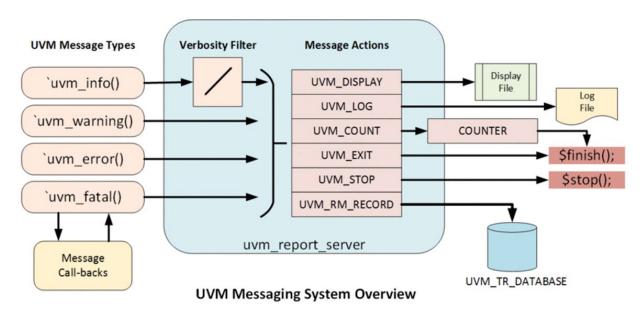

Some messages (e.g., errors) will be more important than others (e.g., progress reports). Therefore, users need the ability to categorize messages by severity:

- Fatal e.g., the simulation has failed and cannot continue

- Error e.g., there is a problem, but simulation can continue

- Warning e.g., there is a possible problem or anticipated issue

- Info e.g., for progress reports

Severity codes allow users to link specific actions with messages, for example, to stop the simulation on a fatal message or after a certain number of error messages. A summary of the messages of each severity at the end of the simulation enables the user to understand the simulation results at a glance. A standalone messaging mechanism for UVM is needed to allow separate control of simulation and simulator reports and to ensure portability, as shown in Figure 16.

Figure 16: UVM messaging system overview

#### 7.2 UVM messaging from the bridge core

It is a requirement to implement UVM messaging from the bridge core. However, reporting macros are not supported in Verilog-AMS modules. A solution to this is via *upwards name referencing*.

For Verilog-AMS files, the `include file "uvm\_ms\_includes.vamsh" defined in this standard, found in Annex A, contains local parameters that define UVM verbosity levels as integers to match the UVM enums. The file "uvm\_ms\_includes.svh" included in the top-level SystemVerilog file of the MS Bridge declares void functions that wrap calls to the uvm\_report\_\*() reporting functions.

Within a digital block of a Verilog-AMS file, users can call `uvm\_ms\_[info|warning|error|fatal] (...) and upwards name referencing finds the corresponding function in the MS Bridge file. See Annex A for more details. SystemVerilog files in the bridge that need to call reporting functions can include either of the two files. The output messages report the file name and the line number from where the reporting function was called. An example is shown below in 7.2.1.

As in `uvm\_info, the user specifies the verbosity in the call to `uvm\_ms\_info. If the verbosity argument is omitted (legal only in SystemVerilog), the default verbosity is UVM\_MEDIUM. The verbosity level for `uvm\_ms\_warning, `uvm ms error, and `uvm ms\_fatal is UVM NONE, as with their regular UVM counterparts.

## 7.2.1 UVM messaging from an AMS bridge core

Calling user-defined non-analog functions is not allowed in a Verilog-AMS analog block, but a solution to invoke messaging is to set a string value and toggle an integer, then use absdelta() to trigger on the toggle and read the string to call `uvm\_ms\_\*(...).

Example:

```

parameter string P__TYPE = "vdriver";

...

//Convert the detection in the analog block to a UVM report.

string message;

always@(absdelta(I thr triggered,1,0,0,1)) begin

```

```

if(I_thr_triggered) begin

$sformat(message,"The Current is above the threshold @ %eA",I_PLUS);

`uvm_ms_info(P__TYPE, message, UVM_MEDIUM)

end

end

```

A typical output message might look like this:

#### 7.2.2 UVM messaging from a DMS bridge core

In principle, a digital core model could use regular UVM messaging, but it is recommended to use the UVM-MS messaging functions for consistency of reported contexts.

#### 8. Testbench

Unlike classical UVM, UVM-MS needs to provide support for designs in a schematic capture tool that require some sort of netlist extraction. To facilitate this, a "dual-top" configuration is suggested. One of the top-level modules, called the <code>test\_bench</code>, encapsulates the physical DUT and MS Bridge components. The other top-level module, called the <code>test\_env</code>, encapsulates the UVM test, environment, agents, etc. This approach allows the <code>test\_env</code> and associated collateral to be different for different netlist extractions of the <code>test\_bench</code>. For example, depending on whether the <code>test\_bench</code> is extracted as AMS or DMS, a different <code>test\_env</code> could be used. In addition, the various schematic capture tools can deal with the complexities of creating design configurations to support instance view bindings.

Figure 17 Dual-top UVM-MS hierarchy

## 9. (informative) Verilog-AMS circuit initialization

#### 9.1 General

Understanding how a Verilog-AMS simulation is initialized can help avoid issues that cause time to debug. The Verilog-AMS standard defines the order, but a simplified description is presented here for convenience.

- 1. Variables are initialized, either to their default values or as specified in a variable declaration assignment. (In this, Verilog-AMS behaves like SystemVerilog, and not like Verilog, where variable declaration assignments execute at the same time as **initial** blocks.)

- 2. **analog initial** blocks execute. These blocks may not contain OOMRs, and the order of execution between **analog initial** blocks in different modules does not matter. These statements occur before the analog matrix is formed, so it is not possible here to probe a voltage, for example. These blocks are used for setting internal variables.

- 3. Digital **initial** and **always** blocks begin to execute in a nondeterministic order until they start to consume time. These blocks may contain OOMRs. So a digital **initial** block may query a value from an analog block. Thus, it is important to ensure that the values of analog variables read in this step are set correctly in step 2.

- 4. At this point, control passes over to the analog solver, which will try to find a DC operating point. Analog DC analysis and the digital simulation at time 0 execute iteratively until all signals at the A/D boundaries reach steady state, which is the DC operating point for transient and AC analysis.

#### 9.2 UVM phases

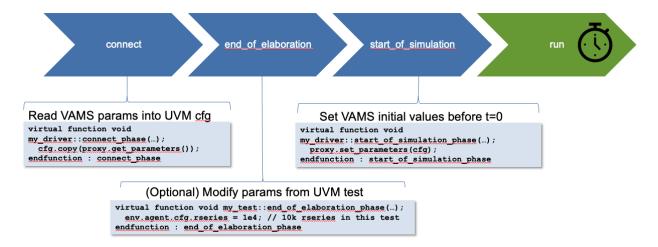

Finding a DC operating point is an iterative process because it will try to converge. This may cause an analog-to-digital event to happen. The RTL code may do something that would then cause a digital-to-analog event that then changes the analog solution. This iteration might have to repeat a few times. The best thing to do is to make sure that the A-to-D or D-to-A boundaries are static. One way to do that is to start the supply zero and then ramp everything up. Assuming all of that works, a DC operating point will be obtained, and the analog solver will choose a point in time to move to and then pass back control to the digital simulator.

This provides an opportunity in the pre-run phases to reconfigure analog parameters. For example, it is possible to change a capacitor value or reconfigure resistors acting as switches to be open or closed before finding a DC operating point. This can be done in a pre-run phase after *build*.

For example, there is a capacitor and it has parameter values on it. In the *connect\_phase*, the parameters can be read into the UVM configuration. The configuration could then be modified in the *end\_of\_elaboration* phase. Finally, in the *start\_of\_simulation* phase, the values on the capacitor can be updated to the values contained in the configuration. In the *run\_phase*, no analog values should be changed until some time has been consumed by the digital simulator (e.g., #1). This ensures that the DC operating point of the circuit is retained.

Figure 18: UVM pre-run phases

## 10. Known limitations

# 10.1 Inout ports on the SystemVerilog interface

Driver-receiver segregation is needed on **inout** connections from the SV IF to the bridge core when the DUT I/O abstraction is a user-defined type or electrical. The current workaround is to split the SV IF port into a driver and receiver manually.

# 10.2 Unpacked array ports on DUT

Using a DUT I/O bus of an unpacked array type, such as an array of real values, prevents swapping the abstraction of the bridge core between DMS and AMS. Verilog-AMS does not yet support unpacked array ports.

## (normative) UVM-MS package and include files

The standard package uvm ms pkg contains the definition of the abstract base proxy class uvm ms proxy.

The MS Bridge and other SystemVerilog files should include the "uvm\_ms\_includes.svh" file in addition to the standard UVM package and include file(s). Verilog-AMS modules in the MS Bridge hierarchy need to include Annex \_ms\_vamsh".

#### A.1 uvm\_ms\_pkg.sv

```

// Proxy class to be extended in the MS Bridge module.

// It allows UVM components to access proxy API by

// passing a handle to the proxy instance via uvm_config_db.

// Class is declared virtual so it cannot

// be instantiated, it must be derived.

`ifndef UVM MS PKG SV

`define UVM MS PKG SV

`include "uvm macros.svh"

package uvm ms pkg;

import uvm pkg::*;

/* uvm ms proxy provides a communication API between driver/monitor and the bridge.

* A proxy specific to the bridge should be created inside the bridge by extending

* uvm ms proxy and then implementing the API functions accordingly.

virtual class uvm ms proxy;

string name;

function new(string name="uvm ms proxy");

this.name = name;

endfunction

// Example prototype for push/pull functions to core

// This function should be added to a derived class and NOT to the uvm ms proxy class

// virtual function void push(input real ampl, bias, freq, bit enable);

`uvm warning("proxy", "Function push not implemented")

// endfunction

// virtual function void pull(output real ampl, bias, freq, bit enable);

`uvm warning("proxy", "Function pull not implemented")

// endfunction

endclass : uvm_ms_proxy

endpackage : uvm ms pkg

`endif

```

#### A.2 uvm\_ms\_includes.svh

```

// various abstractions of the bridge core, e.g., both SV and Verilog-AMS.

// The UVM messaging macros are based on class hierarchy. UVM-MS uses different

// macro names to distinguish them from the UVM macros.

// `uvm ms info works the same as `uvm info except that it passes ` FILE and

// `_LINE_ arguments pass to the info message, reporting where the macro is called,

// typically the bridge core

//

// Output format:

// UVM INFO <file path>(<line number>) @ <time>: reporter <tag> <message>

// ("reporter" is the typical default UVM report handler name

`define uvm ms info(id,message,uvm verbosity) \

uvm_ms_info(id, message, uvm_verbosity, `__FILE__ , `__LINE__);

`define uvm ms warning(id, message) uvm ms warning(id, message, ` FILE , ` LINE );

`define uvm ms error (id, message) uvm ms error (id, message, ` FILE , ` LINE );

`define uvm ms fatal (id, message) uvm ms fatal (id, message, ` FILE , ` LINE );

// The uvm_ms_info function takes arguments from the `uvm_ms_info macro and recreates

// a message identical to `uvm info. This is needed because `uvm ms info is being

// called from a module representing the bridge core and not from a UVM component.

function void uvm ms info(string id, string message, int verbosity, string file,

int line);

uvm report info(id, message, verbosity, file, line);

endfunction: uvm ms info

function void uvm ms warning(string id, string message, string file, int line);

uvm report warning(id, message,, file, line);

endfunction: uvm ms warning

function void uvm_ms_error(string id, string message, string file, int line);

uvm report error(id, message,, file, line);

endfunction: uvm ms error

function void uvm ms fatal(string id, string message, string file, int line);

uvm report fatal(id, message,, file, line);

endfunction: uvm ms fatal

```

#### A.3 uvm ms includes.vamsh

```

// `include file for Verilog-AMS. Not needed for SystemVerilog.

// enums and dynamic objects cannot be accessed via OOMRs,

// so local parameters are used.

// Must be `included within a module scope

localparam integer UVM_NONE = 0;

localparam integer UVM_LOW = 100;

localparam integer UVM_MEDIUM = 200;

localparam integer UVM_HIGH = 300;

localparam integer UVM_FULL = 400;

localparam integer UVM_DEBUG = 500;

// UVM messaging can be called from Verilog-AMS digital code using these functions.

// Via upwards name referencing, the code calls the function in the SystemVerilog

// wrapper layer that then calls the UVM macros (see file "uvm_ms_includes.svh").

```

# (informative) Example: migrating UVM to UVM-MS

#### **B.1 Overview**

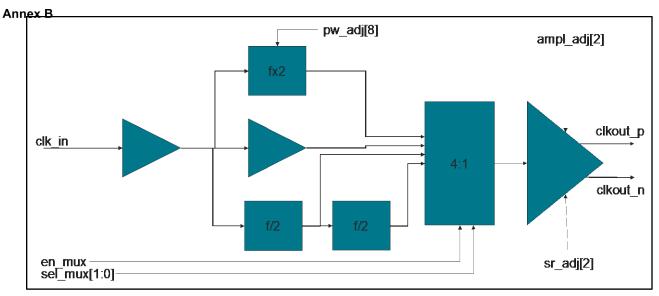

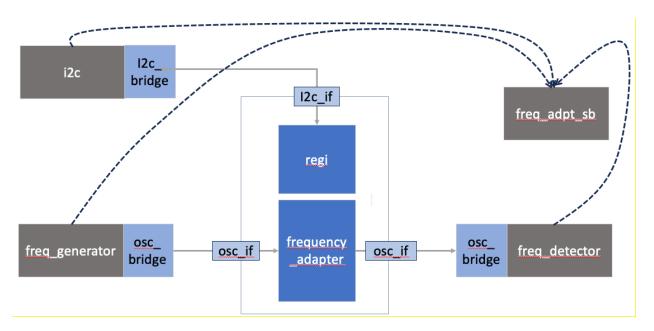

The example presented here is an oscillator agent used to drive and monitor a clock signal to and from a frequency adapter DUT. A block diagram of the DUT is shown in Figure 19:

Figure 19: Frequency adapter DUT

The frequency adapter DUT has a single-ended clock input and a differential clock output. Five control signals modify the clock input to produce the clock outputs: