Community Newsletter: November 2022

IN THIS ISSUE:

- Message from the Chair

- In-person events, updates from our working groups, and more

- Working Group Updates

- CDC Proposed Working Group activity

- IP-XACT tutorial at DVCon Europe focused on revisions to the standard

- Functional Safety Working Group to present a tutorial at DVCon Europe

- UVM-AMS article “Extending the Benefits of UVM to Include AMS”

- Upcoming Events

- DVCon Europe (December 6-7)

- SystemC Evolution Day (December 8)

- Stay tuned for updates on Accellera-sponsored events in 2023

- DVCon U.S. February 27 - March 2

- DVCon Japan 2023 Call For Papers

- Post-Event Summaries

- DVCon India 2022

- SystemC Evolution Fika – videos available!

- Interested in Proceedings from Past DVCon Conferences?

- Videos and more available on demand

- IEEE Get Program Update

- More than 155,000 downloads!

Message from the Chair

It has been encouraging to see more face-to-face meetings and events happening these past few months. DVCon India, held over two days in September, was our first in-person DVCon since the pandemic abruptly halted gatherings. It is another exciting indication that life is getting back to normal.

It has been encouraging to see more face-to-face meetings and events happening these past few months. DVCon India, held over two days in September, was our first in-person DVCon since the pandemic abruptly halted gatherings. It is another exciting indication that life is getting back to normal.

Our work at Accellera has continued in earnest, whether meeting virtually or in person. Our latest Proposed Working Group (PWG) is focused on defining a standard Clock Domain Crossing collateral specification. It held its kickoff meeting in September with a combination of in-person and virtual attendance. There has been a great deal of interest and participation in the PWG from both vendor and user companies, with lively discussion and intriguing proposals during the initial meetings. When the community comes together to brainstorm, great things are bound to happen.

Our existing working groups continue to improve and evolve standards that are important to our community. Updates are coming on the Portable Stimulus Standard 2.0, the SystemC and UVM reference implementations, and SystemC-AMS regression suite. You can also look forward to whitepapers from our Functional Safety and UVM-AMS working groups. And as a result of our close collaboration with IEEE, revisions to IP-XACT were recently approved as IEEE 1685-2022 and our IP Security Assurance Standard 1.0 has moved to the IEEE as IEEE P3164.

Many of you are aware of the signing of the United States CHIPS and Science Act 2022, with a European version around the corner. The implementation of this new law brings with it many challenges as well as great opportunities, such as end-to-end supply chain security and more stringent IP protection requirements. I’d like to welcome our community to come forward with new ideas and proposals that not only safeguard national security but also continue to ensure and promote innovation in our industry.

We hope you’ll join us in Munich for the return of an in-person DVCon Europe and SystemC Evolution Day in early December. With the holidays fast approaching, Munich is especially inviting during this time of year.

I hope to see you soon at one of our Accellera events around the globe.

Wishing you and your colleagues a wonderful holiday season and a happy new year.

Sincerely,

Lu Dai, Accellera Systems Initiative Chair

Working Group Updates

CDC Proposed Working Group

In August Accellera announced the formation of a Proposed Working Group (PWG) to focus on defining a standard Clock Domain Crossing (CDC) collateral specification to ease SOC integration. The PWG held its initial meeting in September to discuss the scope of the PWG. As a result, the group formed four subcommittees:

- Input Collateral: The first committee is focused on input collateral, exploring what should be part of the standard.

- CDC Verification: The scope of the second committee is to define the properties generated with the CDC abstract model and enable them in simulation and formal verification.

- Complex versus Simple Interface: This committee is focused on determining the common standard interfaces used in design and understanding their adoption and the complexity of the CDC and synchronization scheme. This committee will also explore custom interfaces.

- FPGA: This group is tasked with identifying the CDC/RDC (Reset Domain crossing) requirements that are unique to FPGAs and exploring how those requirements could be part of the standard.

The subcommittees have been meeting weekly and presented their recommendations to the CDC PWG on November 2. The next step is to present a final proposal to the Accellera Board of Directors during its upcoming meeting in December.

Participants in the PWG do not need to be from Accellera member companies. For more information on the PWG and how to participate, visit here.

IP-XACT

Accellera’s IP-XACT Working Group has been hard at work developing a proposal for a revision of IEEE Std. 1685-2014. The proposal was handed over to the IEEE P1685 Working Group last year and was approved by IEEE Standards Association Board in September this year.

The working group will present a tutorial at DVCon Europe next month that addresses the main changes in this new revision to the standard. It will also provide examples of tool support from EDA vendors.

The new features supported by the changes between IEEE Std. 1685-2014 and IEEE Std. 1685-2022 include:

- Descriptions of HDL structures, unions and SystemVerilog interfaces in component ports, as well as design connectivity to support these concepts in netlisting.

- Descriptions of analog and mixed-signal properties in component ports to enable mixed-signal netlisting.

- Descriptions of power domains in components and binding of power domains for component instances. This can be used to detect power domain crossings in the connectivity.

- Descriptions of runtime configurable component model parameters that are used by runtime configuration mechanisms such as SystemC CCI.

- Descriptions of parameterized register definitions in addition to register instances to enable reuse of such definitions.

- Descriptions of operating modes in components that affect access of incoming and outgoing transactions, access properties of registers and register fields, and memory remapping.

- Description of register field aliasing and broadcasting.

- Support Representational State Transfer Application (REST) as transport layer for the Tight Generator Interface (TGI)

Some of the major changes will be addressed in greater detail during the tutorial. For more information on the tutorial and to register for DVCon Europe 2022, visit here.

Functional Safety Working Group

The Functional Safety Working Group will present a tutorial during DVCon Europe on Tuesday, December 6 and will also hold a meeting that is open to the community on December 7, as well as a meeting for working group members only on December 8.

DVCon Europe Tutorial abstract: For safety critical applications, standards (e.g., ISO26262) are established to define processes and metrics to comply with Functional Safety requirements.

The implementation of these processes can still pose challenges during the exchange and integration of functional safety data between different work products and activities, carried out by different teams and/or different layers of the supply chain.

Automation tools are now available to support design and verification flows that are functional safety aware, however interoperability among them is not readily available yet.

The Accellera Functional Safety Working Group is defining a language to capture the functional safety data, which is the set of data needed to perform safety activities and to generate work products. The session will provide an update of the activities of the working group. After a brief summary of the industry requirements and challenges, the session will share details about the underlying data model being developed, the formalization process that led to it, and the development process that was followed. It will also include examples of utilization and underlying methodologies. The session will conclude with a brief preview of some future activities to expand the initial data model that has so far focused on FMEDA (Failure Mode Effects and Diagnostic Analysis).

For more information on the tutorial and to register for DVCon Europe 2022, visit here.

In addition to the tutorial presented at DVCon Europe, the Functional Safety Working Group will hold a meeting that is open to the community on December 7 from 9am-12pm & 1:30pm-4:30pm CET at the Synopsys Munich office. Those unable to attend in person can attend via Zoom. To register, visit here.

Following the public meeting, the working group members will meet on December 8 for a full-day session that will also be held at the Synopsys Munich office. For more information on this meeting, please contact Alessandra Nardi, Functional Safety Working Group Chair, via email at Alessandra.Nardi@synopsys.com.

For more information on the Functional Safety Working Group, including recordings from past conference presentations and other resources, visit the working group page.

UVM-AMS Working Group

An article written by working group members Tom Fitzpatrick (WG Chair) and Peter Grove was recently published in Semiconductor Engineering and is republished here.

Extending the Benefits of UVM to Include AMS: An Update on Accellera’s UVM-AMS Standard Development

SoC teams can be divided up into design and verification groups. For digital designs, the Universal Verification Methodology (UVM), initially developed by Accellera and now standardized as IEEE 1800.2, has been the industry standard for the past decade. Since most SoC designs also have analog and mixed-signal IP blocks, it would be ideal for verification engineers to be able to extend the UVM standard to handle Analog/Mixed-Signal (AMS) designs. Accellera has started a Working Group (WG) to create this new standard to benefit AMS designers. As the UVM-AMS standard is adopted by EDA vendors and IP providers, verification IP can be added into a testbench, raising the quality and productivity across chip projects. Reusing verification components and stimuli will boost productivity, and using UVM as a base allows verification engineers to branch into the mixed-signal space. Although the Accellera standard has been labelled UVM-AMS, its focus is on a methodology that will work whether the Device Under Test (DUT) is SPICE, RNM/DMS, or AMS.

AMS simulation involves either a co-simulation of digital-plus-analog solvers, or an event-driven solver for digital-plus-analog real number models.

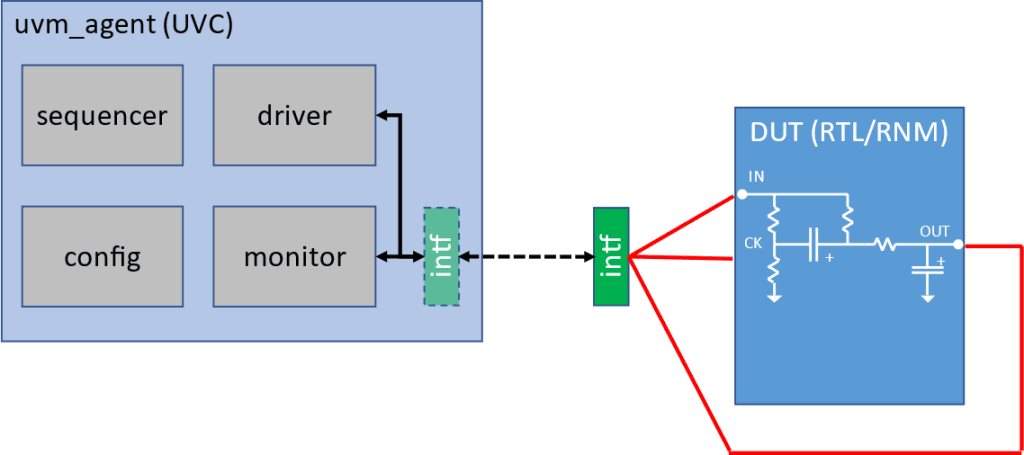

A digital UVM example has a DUT connected to a UVM agent, also called a Universal Verification Component (UVC), using a virtual interface as shown below.

The UVC has several pieces, each with the following roles:

- Sequencer – arbitrates between sequences of transactions

- Driver – controls pins on the virtual interface (intf), based on transactions received from the sequencer

- Monitor – reads responses from the DUT via the intf

- Config – defines behaviors of the sequencer, driver, and monitor

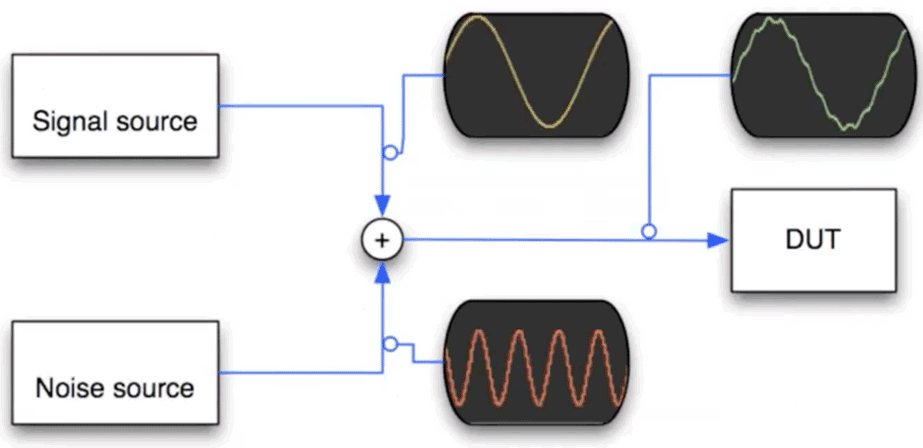

Analog signals, such as sine waves, can be defined in the sequencer by just four values: frequency, phase, amplitude, and DC bias. The UVC for a mixed-signal environment needs to change the function of the driver so it no longer drives the DUT pins directly via the intf, but passes these sine wave properties to a physical module that then applies the stimulus to the DUT pin. This is a break from traditional UVM, but it is required when the DUT pin is mixed-signal. In UVM-AMS, the sequencer will still operate as before, but the driver now generates a request to the new physical module to implement the stimulus.

A more complex signal can be generated by combining an ideal sine wave along with a noise source, as shown below:

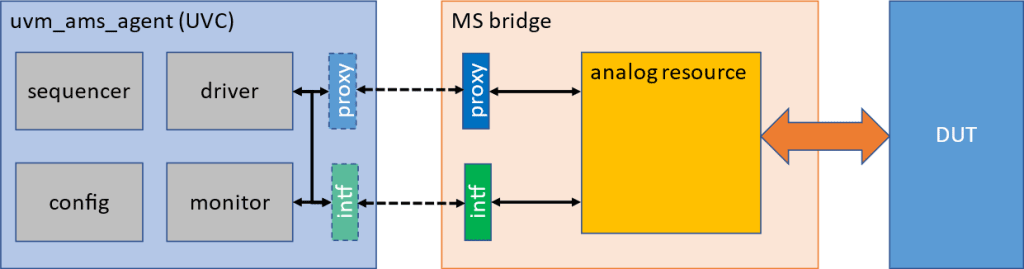

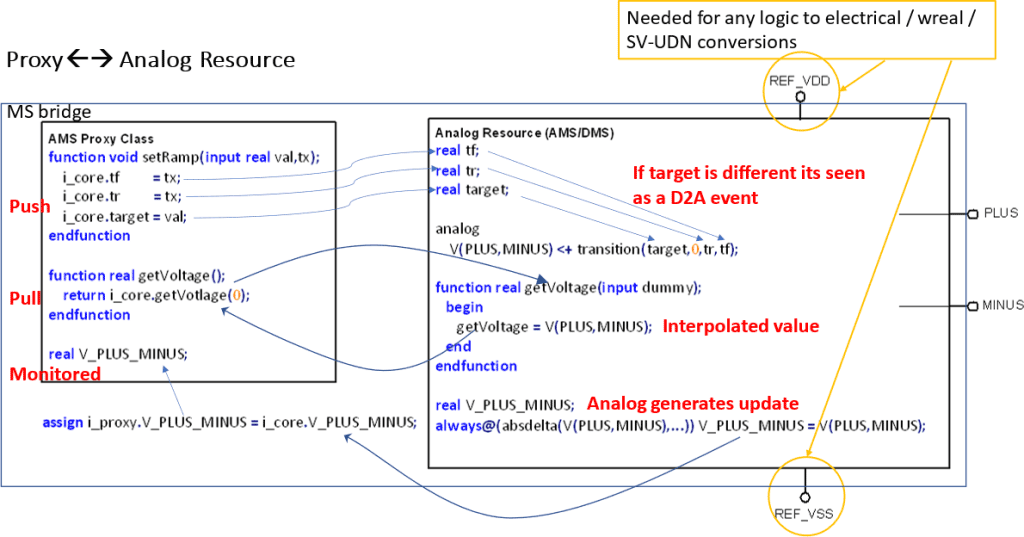

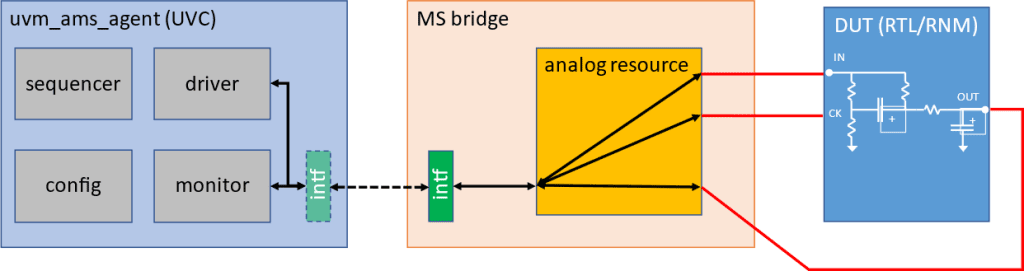

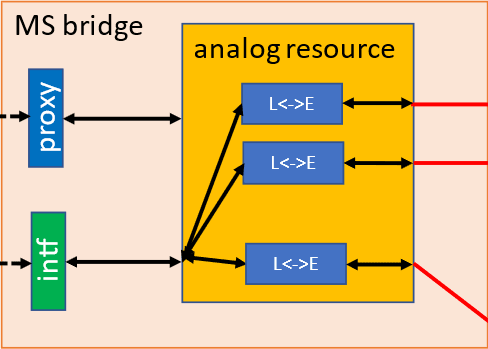

UVM-AMS proposes a Mixed-Signal (MS) Bridge module between the UVC and DUT in order to use continuously varying analog signals required by analog connections to the DUT. The MS bridge is a SystemVerilog (SV) wrapper module with a proxy API, SV interface, and analog resource module. The intf passes the digital and discrete signal values between the UVC and MS bridge. If you’re only driving real numbers, then just the intf is required. Continuous analog signals use the proxy where a request for the stimulus is made by the UVC driver and implemented using the analog resource. The analog resource can be a SystemVerilog or Verilog description if using RNM/DMS on a discrete DUT pin, or a Verilog-AMS description on a continuous electrical DUT pin. The implementation of how to drive out the sine wave is then part of this analog resource module. The example below shows the insertion of the MS bridge and proxy into the traditional UVM environment. The MS bridge SV wrapper serves two purposes: first, it enables SV constructs used by UVM to be used with the Verilog-AMS analog resource; and second, it enables the analog resource to be swapped for a different abstract view without having to change anything else.

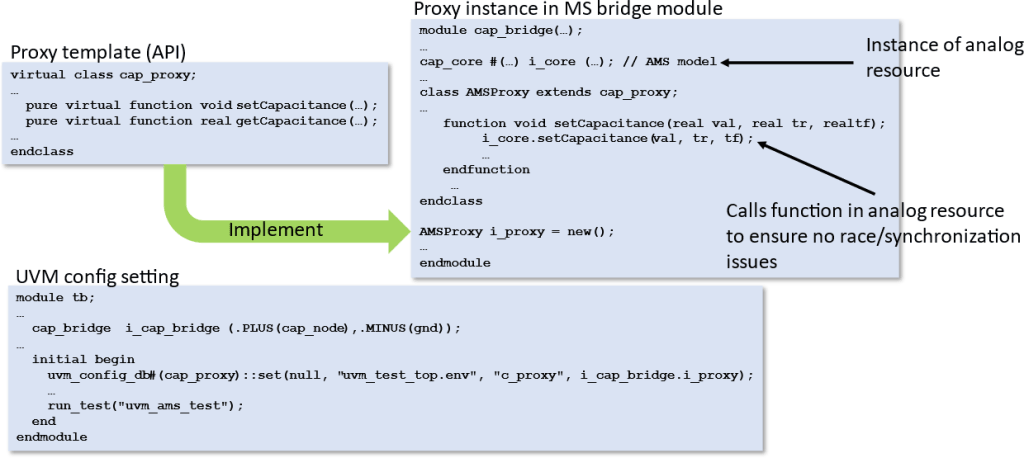

When your testbench requires analog components (capacitor, resistor, inductor, diode, current source, voltage source), you can specify that as Verilog-AMS code in the analog resource, and the components will be controlled by proxy. Here’s an example for setting and getting a capacitance value showing a proxy template API, a proxy instance in the MS bridge module, and a UVM config setting:

The standard proposes four methods to interact with the Verilog-AMS resource, three of which are shown below. The missing one is a way to push the request to change the value but block the return until this change has completed. Within Verilog-AMS, values change from one value to another using a ramp rather than a step change.

Doubler Switch Example

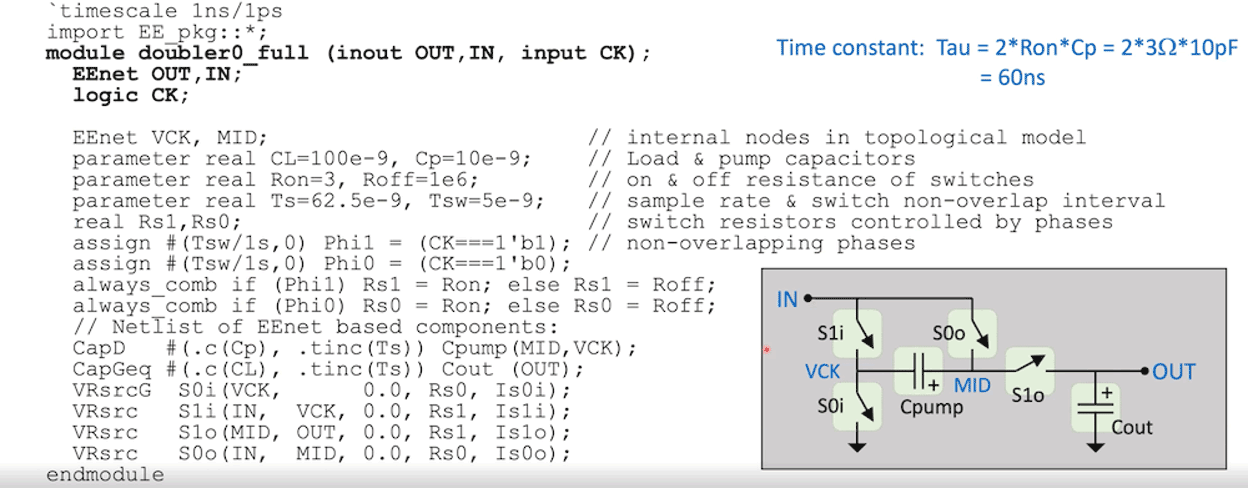

Consider the example of a doubler switch in UVM-AMS using real number modeling (RNM) in our DUT, where only a virtual interface (intf) is required and no proxy. We are driving two inputs (IN, CK) and monitoring one output (OUT).

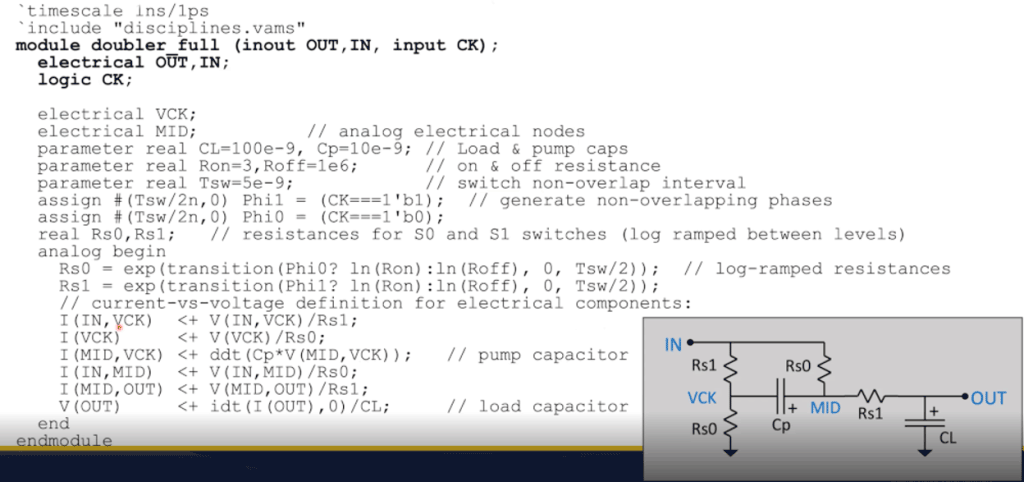

The SystemVerilog code of the DUT using real number modeling is written as:

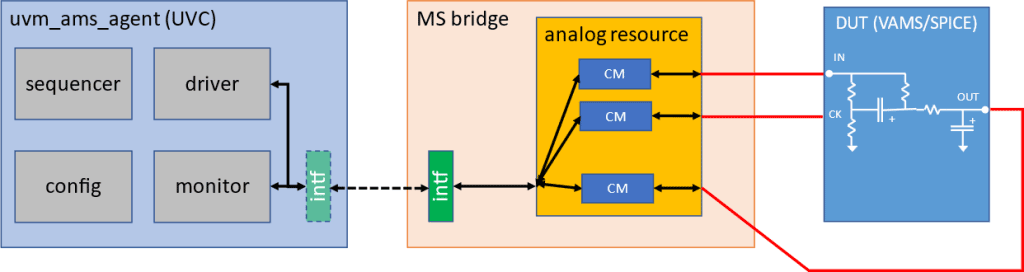

An alternative way to model the same doubler switch in the DUT is by using Verilog-AMS or SPICE; the analog resource in our MS bridge then adds Connect Modules (CM) to interface between analog and digital domains. While this appears the neatest solution, the connect modules now control the transition changes in the value from the intf to the DUT pins, which can’t be controlled by the UVC. In addition, if some pins are current and others voltage (or a mix of the two), then the configuration of the connect modules becomes problematic. For some use cases this might be good enough.

The Verilog-AMS code of the DUT for the doubler switch has the following syntax:

A third option for the doubler switch is adding a proxy to the MS bridge to control the conversion between digital and electrical, while the UVC remains unchanged. Here the analog resource is a custom written module, which via the proxy allows full control of the D2A/A2D boundary.

It’s a best practice when writing code in your analog resource to also use UVM messaging to report information, warnings, errors, and fatal conditions for developers and users of UVM-AMS. The UVM package can’t be imported into a Verilog-AMS module directly, but by using upscoping and the SystemVerilog wrapper (MS bridge), it is possible. This exposes the analog resource to the full potential of the UVM messaging system.

Motivation for UVM-AMS

The planned UVM-AMS standard will encourage support by EDA and IP providers, so they can offer pre-built AMS Verification IP that can be easily integrated into a UVM-AMS testbench. Productivity and quality of AMS verification are the big benefits across new projects through the reuse of proven verification components and stimuli. The UVM-AMS WG is only focused on standards and showing other examples of how to write their own verification IP. In summary, the WG will provide examples of the interactions between the analog and digital engines via the analog resource, as well as the code required to support UVM messaging from a Verilog-AMS module.

UVM has provided our industry great productivity and reuse benefits for digital designs, and the plan is that UVM-AMS will extend those benefits to include a standardized AMS methodology that can scale, is reusable, and promotes metric-driven, mixed-signal verification. During the proposal phase, the design and verification community is invited to influence the specification of UVM-AMS by participating in the working group.

Tom Fitzpatrick, UVM-AMS Working Group Chair

Peter Grove, SystemVerilog AMS Working Group Chair and member of the UVM-AMS Working Group

Upcoming Events

DVCon Europe

The ninth annual DVCon Europe will be December 6-7th at the Holiday Inn Munich-City Centre.

The ninth annual DVCon Europe will be December 6-7th at the Holiday Inn Munich-City Centre.

Registration is open and the advance program is available. The conference will be co-located again this year with SystemC Evolution Day to be held on December 8th.

The keynote speakers for the conference and exhibition are Magnus Oestberg, Chief Software Officer, Mercedes, and Axel Jahnke, Tribe Lead for Nokia SOC L1 ASIC. Mr. Oestberg’s keynote, “Developing the Chip-to-Cloud Architecture for the Most Desirable Cars,” will give insight into Mercedes-Benz’s software strategy focusing on their proprietary operating system as the enabler to create digital luxury. Mr. Jahnke’s presentation “Challenges in SoC Verification for 5G and Beyond,” will discuss some of the approaches to overcome those challenges and the support needed from EDA suppliers.

“We are very pleased to return to an in-person conference and exhibition and are very much looking forward to meeting old friends and new,” stated Sumit Jha, DVCon Europe General Chair. “Our keynotes from industry leaders will once again set the tone for the whole conference: both subjects are highly topical, and the abstracts are intriguing.”

Read the Welcome Letter from Sumit Jha, DVCon Europe 2022 General Chair.

To view videos from DVCon Europe 2021, visit here.

SystemC Evolution Day

The seventh annual SystemC Evolution Day is co-located with DVCon Europe and will be held December 8th at the Holiday Inn Munich-City Centre. It is a full-day technical workshop focused on the evolution of SystemC standards. The 2023 program will focus on SystemC standardization activities and the simulation ecosystem around SystemC.

The seventh annual SystemC Evolution Day is co-located with DVCon Europe and will be held December 8th at the Holiday Inn Munich-City Centre. It is a full-day technical workshop focused on the evolution of SystemC standards. The 2023 program will focus on SystemC standardization activities and the simulation ecosystem around SystemC.

Attendees can register ala carte or as part of DVCon Europe on the registration page for DVCon Europe.

Presentations and videos from SystemC Evolution Day 2021 can be found here.

Stay Tuned for Accellera Events Coming in 2023

DVCon U.S. 2023 Advance Registration Coming Soon!

DVCon U.S. 2023 Advance Registration Coming Soon!

DVCon U.S. 2023 will be in-person February 27-March 2 at the DoubleTree Hotel in San Jose, California. Accellera working groups will present a tutorial focused on Portable Stimulus and workshops on UVM-AMS, SystemC, and IP-XACT.

Advance registration for the 35th annual conference and exhibition will open on November 18 and the program will be available December 5. For the latest updates on DVCon U.S. visit the website.

To view the proceedings from DVCon U.S. 2022, visit here.

DVCon Japan 2023 – Call for Papers Available!

DVCon Japan 2023 – Call for Papers Available!

DVCon Japan is scheduled to be held in-person June 22, 2023, at the Kawasaki City Industrial Promotion Hall in Kawasaki, Kanagawa, Japan. The Call for Papers is now available, and abstracts are due February 20, 2023. For more information and updates, visit the conference website.

Event Updates

For the most recent information on upcoming DVCon conferences around the globe and other Accellera events, visit the Accellera event page.

Post-Event Summaries

DVCon India 2022

“On behalf of the steering committee, I would like to acknowledge all who helped make DVCon India 2022 a grand success! We could see sparkling energy and fervor during our first in-person event post pandemic,” stated Pradeep Salla, DVCon India 2022 General Chair.

“On behalf of the steering committee, I would like to acknowledge all who helped make DVCon India 2022 a grand success! We could see sparkling energy and fervor during our first in-person event post pandemic,” stated Pradeep Salla, DVCon India 2022 General Chair.

“Meeting everyone face-to-face and networking after a gap of three years was exciting! This year we expanded our Steering Committee to extend our reach to academia and help grow university participation,” continued Pradeep. “We also made a conscious effort to expand the reach of DVCon India to include Southeast Asia. We benefited from a very strong team this year which enabled us to bring an exciting agenda which had key takeaways for everyone who participated in the conference. We look forward to seeing everyone in person next year for DVCon 2023!”

For the full conference summary, including highlights and Best Paper and Poster winners, read the press release.

Save the date: DVCon India 2023 will be held September 13-14, 2023 in Bengaluru, India.

SystemC Evolution Fika – Recordings Now Available!

The most recent SystemC Evolution Fika was held in September with a focus on safety-related use cases of SystemC-based virtual prototypes. There were three technical presentations:

The most recent SystemC Evolution Fika was held in September with a focus on safety-related use cases of SystemC-based virtual prototypes. There were three technical presentations:

- “A Fault-Injection Methodology for the System-Level Reliability Analysis of Computing Systems Modeled in SystemC,” presented by Antonio Miele, University Politecnico di Milano, Italy

- “Dynamic Fault Injection with SystemC AMS for Quantitative Safety Verification,” presented by Thomas Markwirth, Fraunhofer IIS/EAS, Dresden, Germany

- “QEMU Based Fault Effect Analysis for RISC-V,” presented by Peer Adelt, Heinz Nixdorf Institut/Universität Paderborn, Germany

For more information, including the abstracts, presentations, and additional recordings from the September 15th session, visit here.

SystemC Evolution Fikas are offered as smaller online workshops. Referred to as fikas to honor the Swedish tradition of sharing a coffee, slowing down a bit, and talking about things that the participants care about. These virtual fikas are free of charge.

If you have topics that you think should be included in an upcoming fika, please email systemc-evolution-fika@lists.accellera.org.

For more information and to view presentations from past fikas, visit the SystemC Evolution event page.

If you’d like more information regarding SystemC, upcoming activities, etc., the SystemC.org community portal is an excellent resource.

Interested in Technical Content from Past DVCon Conferences?

If you’re looking for technical material from recent DVCon conferences-look no further! You can access papers, posters, presentations, and videos from conferences in the U.S., Europe, India, & China here.

IEEE Get Program Update

Since its inception, the Accellera-sponsored IEEE Get Program has resulted in more than 155,000 downloads. The IEEE Get Program provides no cost access of electronic design and verification standards to engineers and chip designers worldwide. For more information and to view the standards available for download, visit the Available IEEE Standards page on the Accellera website.

Accellera Global Sponsors

Contact us if you are interested in becoming a Global Sponsor.

Copyright 2022 Accellera Systems Initiative